(926)274-88-54

Бесплатная доставка.

Бесплатная сборка.

График работы:

Ежедневно. С 8-00 до 20-00.

Почта: soft_hous@mail.ru

|

Звоните! (926)274-88-54 Бесплатная доставка. Бесплатная сборка. |

Ассортимент тканей График работы: Ежедневно. С 8-00 до 20-00. Почта: soft_hous@mail.ru |

|

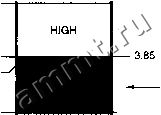

Читальный зал --> Программные средства foundation *3.12. Сопряжение КМОП- и ТТЛ-схем При выборе логического семейства разработчик цифровой аппаратуры по умолчанию руководствуется общими требованиями в отношении быстродействия, потребляемой мощности, стоимости и так далее. Однако в некоторых случаях конструктор может выбирать в качестве элементной базы и другие семейства из-за их доступности или других специальных требований. (Например, не весь ряд схем семейства 74LS имеется в семействе 74НСТ и наоборот) Таким образом, для разработчика важно понимать, как соединяются выходы ТТЛ-схем с входами КМОП-схем и наоборот. При сопряжении ТТЛ- и КМОП-схем следует учесть несколько факторов, и первый из них - запас помехоустойчивости. Запас помехоустойчивости по постоянному току при низком уровне зависит от напряжения дьтах выходе схемы, являющейся источником сигнала, а также от напряжения Vj для входа, подключенного к данному выходу, и равняется У - оьтах очно так же запас помехоустойчивости по постоянному току при высоком уровне равняется q - щп,1 -На рис. 3.84 приведены соответствующие значения для 1СМОП- и ТТЛ-схем. выходы 5.0 0Hmiп OLmax НС, НСТ 3.84 VHC.VHCT З.ВО LS, S, ALS, AS, F 2.7 (изображено не в масштабе) FCT 0.55 LS, S, ALS, AS, F 0.5 VHC, VHCT 0.44 НС, НСТ 0.33  Непредусмотренный 5фовень - 1.35 ВХОДЫ lHmin lLma\ (НС, VHC) Запас помехо- - устойчивости по постоянному току при высоком уровне LS, S, ALS, AS, F, нет VHCT FCT (НС, VHC) LS, S, ALS, AS, F, нет VHCT FCT - Запас помехоустойчивости по постоянному току при НИ.ЗК0М уровне Рис. 3.84. Выходные и входные уровни сигналов, которые необходимо учитывать при сопряжении ТТЛ- и КМОП-схем: HIGH - высокий уровень, LOW- низкий уровень. (Заметьте, что схемы семейств НС и VHC по входу не совместимы со схемами ТТЛ.) Например, запас помехоустойчивости по постоянному току при низком уровне сигнала на входе ТТЛ-схемы, подключенной к выходу одной из схем, принадлежащих семействам НС или НСТ, равен 0.8 В - 0.33 В = 0.47 В, а при высоком уровне сигнала составляет 3.84 В-2.0 В =1.84 В. С другой стороны, запас помехоустойчивости при высоком уровне сигнала на выходе ТТЛ-схемы, нафуженной входами схем серии НС или VHC, равен 2.7 В - 3.85 В =-1.15 В. Другими словами, к выходу ТТЛ-схемы нельзя подключать входы НС- или VHC-схем, если только высокий уровень на выходе какой-то ТТЛ-схемы не окажется выше, а порог высокого уровня на входе у некоторой КМОП-схемы ниже по сравнению со значениями в наихудшем случае, и сумма отклонений не составит 1.15В. Чтобы выходы ТТЛ-схем были правильно согласованы со входами КМОП-схем, КМОП-устройства должны принадлежать семействам НСТ, VHCT или FCT и не быть схемами из семейств НС или VHC. В качестве следующего фактора рассмотрим коэффициент разветвления по выходу. Как и в случае с чистыми ТТЛ-схемами (см. раздел 3.10.3), разработчик должен сложить входные токи устройств, подключенных к выходу, и сравнить результат с возможностями данной схемы по выходу при обоих уровнях выходного сигнала. Если ТТЛ-схема управляет КМОП-схемами, то проблем с коэффициентом разветвления по выходу не возникает, так как входам КМОП-схем при любом уровне сигнала почти не требуется никакого тока. С другой стороны, входам ТТЛ-схем, особенно при низком уровне входного сигнала, требуется значительный ток, по сравнению с возможностями выходных каскадов схем НС и НСТ. Например, к выходу схемы из семейств НС или НСТ можно подключить 10 входов LS-схем или только два входа схем, принадлежащих семейству S-TTL. Последний фактор - величина емкостной нафузки. Мы видели, что емкостная нафузка приводит к увеличению как задержки, так и мощности, рассеиваемой логической схемой. Изменение задержки особенно заметно у схем НС и НСТ, для которых время переходного процесса растет примерно на 1 не при увеличении емкости нафузки на каждые 5 пФ. Транзисторы выходных каскадов схем FCT во включенном состоянии имеют очень малое сопротивление, поэтому для данных схем время переходного процесса растет только на 0.1 не с увеличением емкости нафузки на каждые 5 пФ. При заданной емкости нафузки, напряжении питания и одинаковых условиях эксплуатации, динамическая рассеиваемая мощность у всех КМОП-семейств одна и та же, поскольку значения каждой из переменных, входящих в выражение CVf, одни и те же. С другой стороны, динамическая мощность, рассеиваемая в выходных цепях ТТЛ-схем, несколько меньше из-за меньшего перепада напряжения между высоким и низким уровнями у этих схем. *3.13. Схемы низковольтовой КМОП-логики и их сопряжение с другими схемами Два важных фактора подтолкнули производителей ИС к снижению напряжения питания КМОП-схем: В большинстве случаев сигнал на выходе КМОП-схемы изменяется от потенциала земли до напряжения на шине питания, так что величина Fb выражении CVf равняется напряжению питания. При снижении напряжения питания динамическая рассеиваемая мощность уменьшается еще быстрее. По мере продвижения технологии ко все меньшим размерам транзисторов, изоляция в виде окиси кремния между затвором КМОП-транзистора и стоком и истоком становится все более тонкой и поэтому неспособна выдержать разность потенциалов, доходящую до 5 В, В результате группой промышленных стандартов ИС Обьединенного технического совета по электронным приборам (JEDEC) в качестве очередного стандарта для логических схем были выбраны следующие напряжения питания: З.ЗВ±0.3В,2.5В±0.2В,и1.8В±0.15В. Стандартами JEDEC определены также входные и выходные напряжения логических уровней устройств, работающих с этими напряжениями питания. Переход к меньшим напряжениям происходил постепенно и будет продолжаться дальше. В отношении дискретных логических семейств тенденция состояла в том, чтобы выпускать компоненты с меньшим напряжением питания и с меньшими значениями напряжений на выходах, но допускающие, тем не менее, более высокие напряжения на входах. В следующем разделе мы увидим, что этот подход позволяет КМОП-схемам с напряжением питания 3.3 В работать совместно с 5-воль-товыми КМОП- и ТТЛ-схемами. Подобный подход использован во многих специализированных интегральных схемах и микропроцессорах, но часто применяется также и другой метод. Упомянутые устройства достаточно велики, так что имеет смысл снабдить их двумя источниками питания. Низкое напряжение, скажем 2.5 В, служит питанием для внутренних узлов микросхемы, логического ядра {core logic). Большее напряжение, например 3.3 В, используется для питания внешних цепей ввода и вывода, образующих интерфейсный блок {padring), посредством которого осуществляется сопряжение со схемами старшего поколения, примененными в системе. Для быстрого и безошибочного преобразования логических уровней между логическим ядром и интерфейсным блоком применяются специальные буферные схемы. *3.13.1. LVTTL- и ЬУСМОЗ-логика с напряжением питания 3.3 В Нарис. 3.85 наглядно представлены соотношения между уровнями сигналов для обычных ТТЛ-семейств и низковольтовых КМОП-схем, работающих при своих номинальных напряжениях питания; эти соотношения взяты из указаний по применению фирмы Texas Instruments. Исходные симметричные уровни сигнала для чисто 5-вольтовых КМОП-семейств типа НС и VHC показаны на рис. 3.85(a). В КМОП-схемах, совместимых с ТТЛ-схемами, таких как НСТ, VHCT и FCT, уровни напряжения сдвинуты вниз, как показано на рис. 3.85(b). Первым шагом на пути уменьшения напряжения питания КМОП-схем стало напряжениеЗ.З В. Фактически стандарт JEDEC для 3.3-вольтовой логики определяет два набора уровней. Уровни LVCMOS {низковольтовыеуровни КМОП-схем; low-voltage CMOS) относятся к случаю использования только КМОП-схем, когда выходы схем слабо нагружены по постоянному току (меньше 100 мкА), так что напряжения OL он отличаются от потенциала земли и от напряжения питания не более, чем на 0.2 В. Уровни LVTTL {низковапьтовые уровни схем, совместимых с ТТЛ; low- ООО «Мягкий Дом» - это Отечественный производитель мебели. Наша профильная продукция - это диваны еврокнижка. Каждый диван можем изготовить в соответствии с Вашими пожеланияи (размер, ткань и материал). Осуществляем бесплатную доставку и сборку. Звоните! Ежедневно! (926)274-88-54 Продажа и изготовление мебели. Копирование контента сайта запрещено. Авторские права защищаются адвокатской коллегией г. Москвы. |