(926)274-88-54

Бесплатная доставка.

Бесплатная сборка.

График работы:

Ежедневно. С 8-00 до 20-00.

Почта: soft_hous@mail.ru

|

Звоните! (926)274-88-54 Бесплатная доставка. Бесплатная сборка. |

Ассортимент тканей График работы: Ежедневно. С 8-00 до 20-00. Почта: soft_hous@mail.ru |

|

Читальный зал --> Программные средства foundation 74x08 0(0.71 ERROR 74x260 74x08 >

IRP 4 4> 2 RD L Микросхема памяти READ WRITE DINO 0IN1 DIN2 DIN3 0IN4 DINS DIN6 DIN7 DOUTO D0UT1 ооитг D0UT3 D0UT4 D0UT5 DOUTe D0UT7 POUT 74x541

О Gl A2 A3 A4 A5 AO A7 A8

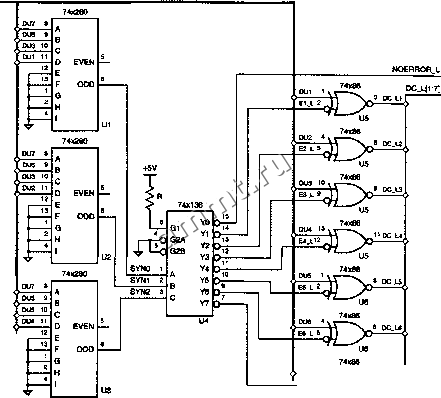

Рис. 5.76. Формирование бита четности и проверка на четность для 8-разрядной системы памяти Чтобы извлечь байт, мы задаем адрес (не показанный на рисунке) и подаем сигнал чтения RD; значение байта появляется на выходах DOUT[0-7], а бит четности - на выходе POUT. Микросхема 74x541 выполняет роль буфера при передаче байта на шину D, а микросхема 280 осуществляет проверку на четность. Если при чтении проверка на четность 9-разрядного слова DOUT[0-7], РОиТдает нечетное число единиц, то вырабатывается сигнал ошибки ERROR. Схемы проверки на четность применяются также при работе с кодами, исправляющими ошибки, такими как коды Хэмминга, описанные в разделе 2.15.3. На рис. 2.13 бьша приведена матрица проверки на четность для 7-разрядного кода Хэмминга. Ошибки, возникающие в этом коде, можно исправлять так, как показано на рис. 5.77. На шине DU[1 -7] присутствует 7-разрядное слово, возможно содержащее ошибки. С помощью трех микросхем 74x280 проверяется четность в трех 4-битовых группах, указываемых проверочной матрицей. На выходах микросхем 280 формируется синдром, которым определяется номер ошибочного входного бита, если таковой имеется. Микросхема 74x138 используется для декодирования синдрома. Если синдром равен нулю, то вырабатывается сигнал NOERR0R L (этот сигнал можно было бы назвать также ERROR). В противном случае ошибочный бит исправляется путем его инвертирования. Исправленное кодовое слово появляется на шине DC L. Заметим, что из-за низкого активного уровня сигналов на выходах микросхемы 138 сигналы на шине DC L также имеют низкий активный уровень. Если необходима шина DC с высоким активным уровнем сигналов, то на входе или выходе каждой из схем ИСКЛЮЧАЮЩЕЕ ИЛИ можно поместить отдельный инвертор, либо воспользоваться дешифратором с высоким активным уровнем сигналов на выходах, либо использовать схемы ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ. DU[1:7]  Рис. 5.77. Схема, исправляющая ошибки в 7-разрядном коде Хэмминга 5.8.5. Описание схем ИСКЛЮЧАЮЩЕЕ ИЛИ и схем проверки на четность на языке ABEL и их реализация в ПЛУ в языке ABEL функщпо ИСКЛЮЧАЮЩЕЕ ИЛИ реализует оператор $, а дополнение этойфункции-ИСКЛЮЧАЮЩЕЕИЛИ-НЕ-обозначается !$. В принципе,употребление этих операторов в выражениях на языке ABEL ничем не ограничено. Вы можете, например, задать сигнал на выходе ПЛУ, эквивалентный сигналу even на выходе ИС 74x280, следующим вьфажением на языке ABEL: EVEN = !(A$B$C$D$E$F$G$H$I). Однако в большинстве ПЛУ выражения реализуются посредством двухуровневой логики И-ИЛИ и лишь в малой степени могут напрямую реализовать функцию ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ, если такая возможность вообще имеется. К сожалению, карта Карно и-входовой схемы ИСКЛЮЧАЮЩЕЕ ИЛИ выглядит как шахматная доска с 2 простыми импликантами. Поэтому для реализации приведенного выше Табл. 5.46. Потоковая VHDL-программа для 3-входовой схемы ИСКЛЮЧАЮ- -Г ЩЕЕИЛИ use IEEE.std logic l164.all; entity vxor3 IS port ( A, B. C: m STD.LOGIC; Y: out STD.LOGIC end vxor3; architecture vxorS of vxorS is begin Y <= A xor В xor C; end vxorS; Когда синтезируется схема ИСКЛЮЧАЮЩЕЕ ИЛИ с большим числом входов, описанная на языке VHDL, программные средства наилучшим образом используют технологию, по которой выполнено ПЛУ, для реализации этой функции. И нет ничего удивительного в том, что при попытке указать VHDL-программе, приведенной в табл. 5.47, в качестве ПЛУ ИС 16V8 средства синтеза признают ее непригодной! простого соотношения средствами, рассчитанными на выражения вида сумма произведений , потребовалось бы 256 термов-произведений, что находится за пределами возможностей любого ПЛУ. В ПЛУ так называемой серии X двухвходовую схему ИСКЛЮЧАЮЩЕЕ ИЛИ можно реализовать непосредственно трехуровневой структурой, в которой с помощью одного вентиля ИСКЛЮЧАЮЩЕЕ ИЛИ объединяются два независимых выражения вида сумма произведений . Такая структура оказывается полезной при построении счетчиков. Однако для создания больших схем ИСКЛЮЧАЮЩЕЕ ИЛИ при проектировании на уровне платы обычно бывает необходимо воспользоваться специализированным узлом формирования проверочного символа и проверки на четность типа 74x280, а разработчик специализированных ИС должен составлять из отдельных схем ИСКЛЮЧАЮЩЕЕ ИЛИ многоуровневое дерево проверки на четность, подобное тому, которое показано на рис. 5.74(b). 5.8.6. Описание схем ИСКЛЮЧАЮЩЕЕ ИЛ И и схем проверки на четность на языке VHDL Подобно языку ABEL, в языке VHDL имеются примитивы хог и xnor, реализующие функции ИСКЛЮЧАЮЩЕЕ ИЛИ и ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ (оператор xnor имеется только в версии языка VHDL-93). В табл. 5.46 в качестве примера приведена программа в потоковом стиле для 3-входового устройства ИСКЛЮЧАЮЩЕЕ ИЛИ, где использован примитив хог. Можно также создавать схемы ИСКЛЮЧАЮЩЕЕ ИЛ И и схемы проверки на четность, описывая их поведение, как это сделано в табл. 5.47 для 9-входовой схемы проверки на четность, аналогичной ИС 74x280. ООО «Мягкий Дом» - это Отечественный производитель мебели. Наша профильная продукция - это диваны еврокнижка. Каждый диван можем изготовить в соответствии с Вашими пожеланияи (размер, ткань и материал). Осуществляем бесплатную доставку и сборку. Звоните! Ежедневно! (926)274-88-54 Продажа и изготовление мебели. Копирование контента сайта запрещено. Авторские права защищаются адвокатской коллегией г. Москвы. |

|||||||||||||||||||||||||||||||||||||||||||