(926)274-88-54

Бесплатная доставка.

Бесплатная сборка.

График работы:

Ежедневно. С 8-00 до 20-00.

Почта: soft_hous@mail.ru

|

Звоните! (926)274-88-54 Бесплатная доставка. Бесплатная сборка. |

Ассортимент тканей График работы: Ежедневно. С 8-00 до 20-00. Почта: soft_hous@mail.ru |

|

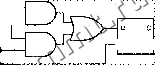

Читальный зал --> Программные средства foundation чение, схема ведет себя как обычный D-триггер. Когда же подан сигнал ТЕ, разрешающий тестирование, триггер берет данные с входа Т1 {test input, тестовый вход), а не с входа D. Таблица, описывающая работу схемы, представлена на рис. (Ь), а условное обозначение данного устройства - на рис. (с). D D-Tt 0-т-О  ТЕ Т1 D CLK Q 1 1 О X О J О 1 0 X 1 J~ 1 О 1 О X J~ О 1 Г 1 о 0 laslQ laslQN 1 las! Q last QN D ТЕ Tl - >0LK Рис. 7.22. Тестируемый D-триггер, переключающийся по положительному фронту: (а) принципиальная схема; (Ь) таблица, описывающая работу схемы (last - последнее значение); (с) условное обозначение Дополнительные входы используются для соединения всех триггеров в специализированной ИС с целью тестирования в одну цепочку сканирования (scan chain). На рис. 7.23 приведен простой пример цепочки сканирования, состоящей из четырех триггеров. Входы ТЕ всех триггеров объединяются вместе в один глобальный вход ТЕ, тогда как выход Q каждого триггера соединяется с входом Т1 другого триггера, образуя последовательную цепочку (daisy chain). Соединения, относящиеся ко входам Т1 и ТЕ, а также к выходу ТО (test output, тестовый выход), предназначены исключительно для целей тестирования; другие соединения, относящиеся ко входам D и выходам Q, необходимые для того чтобы схема в целом могла делать что-то полезное, на рисунке не показаны. внешние выводы специализированная ИС CLKQ - О- [- >CLK >CLK а то Рис. 7.23. Цепочка сканирования из четырех триггеров Для того чтобы протестировать схему, в том числе и основную логику, разрешающий сигнал удерживается на глобальном входе ТЕ в течение п периодов тактового сигнала, в то время как через глобальный вход Т1 в и триггеров посредством сдвига загружается и-разрядный тестовый вектор; на рис. 7.23 число п равно 4. Затем сигнал ТЕ снимается и схеме предоставляется возможность функционировать в течение одного или нескольких следующих тактов. Новое состояние схемы. представленное новыми значениями сигналов на выходах п триггеров, можно считать, наблюдая сигнал на выходе ТО в течение очередных п тактов при условии, что на входе ТЕ действует разрешающий сигнал. После того как результаты одного тестирования прочитаны, можно зафузить другой проверочный вектор; такая возможность делает процесс тестирования более эффективным. Существует столько различных типов тестируемых триггеров, сколько имеется различных способов реализации самих триггеров. Например, возможностью тестирования мог бы быть наделен D-триггер с входом разрешения, изображенный на рис. 7.21, путем замены его 2-входового внутреннего мультиплексора на 3-входовой. Тогда, в зависимости от значений сигналов EN и ТЕ, в триггеры на каждом такте записывались бы сигналы с входов D или Т1 или его собственное текущее состояние. Возможность тестирования можно добавить также и в случае триггеров других типов, в частности JK-триггеров и Т-триггеров, о которых речь пойдет позднее в этом параграфе. *7.2.8. Двухтактный SR-триггер Как указывалось ранее, SR-защелки полезны в управляющих устройствах , где возможны независимые условия установки и снятия контрольного бита. Если предполагается, что контрольный бит должен меняться только в определенные моменты времени, привязанные к тактовому сигналу, то нужен SR-триггер, подобный D-триггеру, у которого сигналы на выходах изменялись бы только на определенном перепаде тактового сигнала. В этом и в двух следующих разделах описаны триггеры, полезные при решении таких задач. Если D-защелки в D-триггере, переключающемся по отрицательному фронту [рис. 7.18(a)], заменить SR-защелками, то получим двухтактный SR-триггер {master/slave S-R flip-flop; триггер, действующий по принципу ведущий-ведомый), показанный на рис. 7.24. Аналогично D-триггеру, выходные сигналы SR-триггера изменяются только по спадающему фронту в тактовом сигнале С. Однако новое значение выходного сигнала зависит теперь не от значений входных сигналов точно в тот момент времени, на который приходится спадающий фронт, а от значений входных сигналов на протяжении всего интервала времени, в течение которого сигнал С был равен 1 перед отрицательным перепадом. Как следует из временных диафамм на рис. 7.25, короткий импульс S в любом месте в пределах указанного интервала времени может установить ведущую защелку в единичное состояние; точно так же импульс на входе R может сбросить ее. Значение, переносимое на выход триггера в момент действия спадающего фронта в сигнале С, зависит от того, каким было последнее состояние ведущей защелки, пока сигнал С оставался равным 1. Согласно рис. 7.24(c), в условном обозначении двухтактного SR-триггера не используется указатель динамического входа, поскольку этот триггер не является истинно переключающимся по фронту. Он скорее похож на защелку, в которой происходит повторение ее входного сигнала в течение интервала времени, на котором С равняется 1, но изменения сигнала на выходе триггера отражают конечное защелкнутое значение только тогда, когда С становится равным 0. На тот факт, что выходной сигнал не изменяется до тех пор, пока сигнал на входе разрешения С не перейдет на неактивный уровень, указывает индикатор задержки срабатывания {postponecl-output indicator) в условном обозначении. Триггеры, ведущие себя таким образом, иногда называют триггерами со срабатыванием по импульсу (pulse-triggered flip-flops). s о- (JM L - -0--а QN

Рис. 7.24. Двухтактный SR-триггер: (a) схема на SR-защелках; (b) таблица, описывающая работу схемы (last - последнее значение; undef. - неопределенное значение); (с) условное обозначение Игнорируется, так как С равно нулю ; П Игнорируется до тех пор, пока С не станет равным 1 Игнорируется до тех пор, пока С не станет равным 1

Рис. 7.25. Временные диаграммы, иллюстрирующие работу двухтактного SR-триггера Работа двухтактного SR-триггера оказывается непредсказуемой, если в момент отрицательного перепада в сигнале С оба входных сигнала S и R имеют активный уровень. В этом случае к моменту действия спадающего фронта оба выходных сигнала ведущей защелки Q и QN равны 1. Когда сигнал С становится равным О, значения сигналов на выходах ведущей защелки предсказать нельзя; более того, ее выходная цепь может оказаться метастабильной. В то же самое время ведомая защелка открывается и весь этот мусор проходит на выход триггера. *7.2.9. Двухтактный JK-триггер Проблема с тем, что делать, когда одновременно действуют сигналы S и R, решается в двухтактном Ж-триггере (master/slave J-K flip-flop). Входы J и К аналогичны входам 8 и R. Однако, как видно из рис. 7.26, сигнал J попадает на вход S ведущей защелки только в том случае, когда текущее значение сигнала на выходе триггера QN равно I (то есть сигнал Q равен 0), а сигнал К попадает на ООО «Мягкий Дом» - это Отечественный производитель мебели. Наша профильная продукция - это диваны еврокнижка. Каждый диван можем изготовить в соответствии с Вашими пожеланияи (размер, ткань и материал). Осуществляем бесплатную доставку и сборку. Звоните! Ежедневно! (926)274-88-54 Продажа и изготовление мебели. Копирование контента сайта запрещено. Авторские права защищаются адвокатской коллегией г. Москвы. |