(926)274-88-54

Бесплатная доставка.

Бесплатная сборка.

График работы:

Ежедневно. С 8-00 до 20-00.

Почта: soft_hous@mail.ru

|

Звоните! (926)274-88-54 Бесплатная доставка. Бесплатная сборка. |

Ассортимент тканей График работы: Ежедневно. С 8-00 до 20-00. Почта: soft_hous@mail.ru |

|

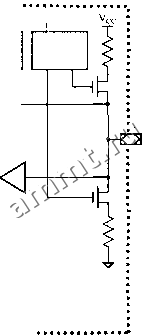

Читальный зал --> Программные средства foundation 16x1, а схема Н представляет собой статическое ОЗУ 8x1. Когда логический блок используется для выполнения логических операций, при формировании его структуры в статическое ОЗУ из внешнего ПЗУ зафужаются таблицы истинности логических функций F, G и Н. Профаммирование мультиплексоров, указанных на рис. 10.44, также осуществляется путем зафузки ячеек памяти, представляющих собой отдельные D-защелки, управляющие мультиплексорами; информация в них тоже заносится при конфигурировании ИС. Такого рода профаммирование выполняется для всех логических блоков, входящих в состав ИС типа FPGA. Помимо удобства профаммирования, применение памяти для хранения таблиц истинности имеет другое важное достоинство. Любой логический блок в микросхеме серии ХС4000 при запуске можно сконфигурировать так, чтобы использовать его в качестве памяти, а не логики. Возможны несколько разных режимов формирования структуры логического блока: Два статических ОЗУ 16У.1. Схемы F и G используются в качестве статических ОЗУ с независимыми адресными входами и входами записываемых данных. Однако вход разрешения записи у них общий. Одно статическое ОЗУ 32x1. Одни и те же четыре адресных бита подаются на входы схем F и G, а пятый адресный бит, поступающий на схему Н и на схему разрешения записи, позволяет выбирать между верхней и нижней половинами памяти F и G. Асинхронный или синхронный режим работы. Структура упомянутых выше статических ОЗУ может быть сформирована так, чтобы при записи происходила нормальная асинхронная фиксация данных, либо запоминание данных осуществлялось по заданному фронту тактового сигнала К. Одно статическое ОЗУ 16x1 с двумя портами. Возможно независимое выполнение чтения и записи для двух разных ячеек одного и того же статического ОЗУ по двум наборам сигналов на адресных входах. В данном режиме поддерживаются только синхронные операции записи. В этих режимах сигналы на функциональных входах F1-F4 и G1-G4 играют роль адреса, а на входы Н0-Н2 логического блока подаются данные и сигнал разрешения записи; сигналы данных, появляющиеся на выходах F и G, можно запомнить в триггерах FF1 и FF2 или вывести на вьеходы X и Y данного логического блока. 10.6.3. Блок ввода/вывода Структура блока ввода/вывода {I/O block, IOB) в ИС семейства ХС4000 показана на рис. 10.45. I/0-вывод можно использовать в качестве входа или выхода, либо в качестве того и другого. У блока ввода/вывода в микросхемах семейства ХС4000 больше средств логического управления, чем у его ближайшего родственника в ИС типа CPLD семейства ХС9500. В частности, на пути входного и выходного сигналов имеются переключающиеся по фронту D-триггеры, возможность записи в которые определяется мультиплексорами М5-М7. Размещение входного и выходного триггеров рядом с I/0-выводами является особенно полезным свойством ИС типа FPGA. Относительно большие задержки при прохождении сигналов от выходов внутренних триггеров логических блоков до блоков ввода/вывода могут затруднить стыковку данной ИС со стороны ее выходов с внешними синхронными системами, если частота тактового сигнала очень высока. Большие задержки от I/ 0-выводов до входов триггеров в логических блоках могут затруднить сопряжение данной ИС со стороны ее входов с внешней системой с точки зрения удовлетворения требованиям по времени установления и времени удержания, если внешние входные сигналы поступают непосредственно на тактовые входы триггеров внутри логических блоков, а не фиксируются сначала триггерами в блоках ввода/вывода. Конечно, применение триггеров в блоках ввода/вывода возможно только в том случае, когда технические требования к внешнему интерфейсу ИС типа FPGA допускают конвейерный режим работы по входам и выходам. Включение резистора между выходом и шимой питания или землей OUT-OCLK- ICLKEN-ICLK- Блок ввофвода Управление ааэростыо нарастания -сигнала <1

Выходной Q D CLK< EN Задержка  Входной буфер Рис. 10.45. Блок ввода/вывода в ИС семейства ХС4000 Чтобы обеспечить конвейерный режим работы по входу в блоке ввода/вывода ИС серии ХС4000 фактически делается еще один шаг в этом направлении: с помощью мультиплексора М8 на пути к D-входу входного триггера FF2 может быть введена задержка. Действие этого элемента заключается в задержке сигнала на D-входе относительно копий системных тактовых сигналов внутри данной ИС, гарантирующей, что время удержания по входу относительно внешнего тактового сигнала будет равно нулю. Этот режим достигается, конечно, за счет увеличения времени установления. Другой возможностью логического управления в блоке ввода/вывода является выбор - с помощью мультиплексоров М1 -М4 - полярности четырех входных сигналов, поступающих из матрицы логических блоков по структуре программируемых соединения. Этими входными сигналами являются: выходной бит OUT, сигнал разрешения Т, открывающий выход с тремя состояниями, выходной тактовый сигнал OCLK и сигнал разрешения ICLKEN по тактовому входу. Подобно блокам ввода/вывода в микросхемах серии ХС9500, в блоках ввода/ вывода микросхем серии ХС4000 возможно управление аналоговыми параметрами выходного сигнала. Можно запрофаммировать скорость изменения сигнала, вырабатываемого выходным буфером, а между I/0-выводом и шиной питания или землей можно включить резистор. 10.6.4. Программируемые соединения Итак, лучшее мы оставили напоследок. Архитектура профаммируемых соединений в микросхемах серии ХС4000 - прекрасный пример структуры, обеспечивающей богатые возможности образования необходимых связей и занимающей небольшую площадь на поверхности кремниевого кристалла. Как показано нарис. 10.43, каждый логический блок в ИС типа FPGA окружен структурой соединений, которая в действительности является всего лишь совокупностью проводов с возможностью подключения к ним посредством соответствующего профаммирования. Нарис. 10.46 структура соединений в ИС серии ХС4000 изображена немного подробнее. Сигнальные линии действительно не являются собственностью какого-либо одного логичесюго блока, а матрица логических блоков внутри ИС представляет собой мозаику, составленную точно из таких структур, какая показана на рисунке. Например, 100-кратное повторение этого рисунка дает матрицу логических блоков микросхемы ХС4003 размером 10x10. /\ /\ /\ /\ its. 6 4 6 4 2 \У <7 О О о Дальняя Связь Связь с Общий Непосред- связь через соседним тактовый ственное блок блоком сигнал соединение ~8~% Связь С соседним блоком ~4~ Связь через блок Дальняя связь Г Непосредственное соединение :J> Дал1 ьняя связь Рис. 10.46. Общая структура соединений в микросхемах серии ХС4000 ООО «Мягкий Дом» - это Отечественный производитель мебели. Наша профильная продукция - это диваны еврокнижка. Каждый диван можем изготовить в соответствии с Вашими пожеланияи (размер, ткань и материал). Осуществляем бесплатную доставку и сборку. Звоните! Ежедневно! (926)274-88-54 Продажа и изготовление мебели. Копирование контента сайта запрещено. Авторские права защищаются адвокатской коллегией г. Москвы. |