(926)274-88-54

Бесплатная доставка.

Бесплатная сборка.

График работы:

Ежедневно. С 8-00 до 20-00.

Почта: soft_hous@mail.ru

|

Звоните! (926)274-88-54 Бесплатная доставка. Бесплатная сборка. |

Ассортимент тканей График работы: Ежедневно. С 8-00 до 20-00. Почта: soft_hous@mail.ru |

|

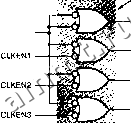

Читальный зал --> Программные средства foundation CLOCK L  все в одном - корпусеИС CLOCK GCLK1 GCLK2 GCLK3 CLOCK L CLOCK CLKEN GCLK Рис.8.90. Приемлемый способ стробирования тактового сигнала: (а) схема; (Ь) временные диаграммы 8.8.3. Асинхронные входы Хотя теоретически можно построить полностью синхронный компьютер, вы вряд ли сможете им воспользоваться, если только не окажетесь способным нажимать на клавиши синхронно с 500-мегагерцным тактовым сигналом. Цифровой системе любого типа всегда приходится иметь дело с асинхронными входными сигналами {asynchronous input signals), которые не привязаны к тактовому сигналу системы. Асинхронные входные сигналы часто бывают запросами на обслуживание (например, прерывания в компьютере) или признаками возникновения тех или иных условий (например, сигнал о том, что какой-то ресурс стал доступен). Обычно такие сигналы изменяются медленно по сравнению с тактовой частотой системы, и нет необходимости распознавать их на определенном такте. Если переход в таком сигнале будет пропущен на данном такте, его всегда можно обнаружить на следующем. Скорость переключений асинхронных сигналов может простираться от одного изменения в секунду (когда за клавиатурой сидит медлительный человек) до 100 МГц и более (запрось[ на доступ к совместно используемой памяти в 500-мегагерцной многопроцессорной системе). Если не принимать во внимание проблему метастабильности, то нетрудно построить синхронизирующее устройство {synchronizer), то есть схему, в которой будет браться выборка асинхронного входного сигнала и вырабатываться выходной сигнал, удовлетворяющий требованиям синхронной системы по времени установления и времени удержания. Как видно из рис. 8.91, D-триггер берет выборки асинхронного входного сигнала на каждом такте системного тактового CLOCK- низкий). Таким образом, запас по времени будет зависеть от коэффициента заполнения тактового сигнала особенно тогда, когда сигнал CLKEN оказывается значительно сдвинутым по отношению к переключаюшему фронту тактового сигнала из-за большой задержки в комбинационной логике (t ) п comb- настоящей синхронной системе входной сигнал разрешения выполнения той или иной функции может изменяться почти в любой момент времени в пределах всего периода тактового сигнала вплоть до границы времени установления перед переключающим фронтом тактового сигнала; такого рода решение применительно к разрешению загрузки ИС 74x377 приведено на рис. 8.13. сигнала и вырабатывает синхронный выходной сигнал, значение которого удерживается в течение следующего периода тактового сигнала. ASYNCIN- (асинхронный входной сигаал) синхронизирующее устройство SYNCIN CLOCK D Q >CLK (системный тактовый сигнал) CLOCK ASYNCIN SYNCIN Синхронная система Рис. 8.91. Простое синхронизирующее устройство на одном D-триггере: (а) схема; (Ь) временные диаграммы синхронизирующие устройства SYNC1 ASYNON- (асинхронный входной сигаал) D Q >CLK CLOCK - >CLK (системный тактовый сигнал) CLOCK ASYNCIN SYNC1 SYNC2 SYNC2 Синхронная система Рис. 8.92. Два синхронизирующих устройства для одного и того же асинхронного входного сигнала: (а) схема; (Ь) возможные временные диаграммы Для асинхронных входных сигналов существенно, чтобы их привязка к тактовому сигналу производилась в системе только в одном месте; на рис. 8.92 показано, что может произойти в противном случае. Из-за физических задержек в схеме два триггера не видят тактовый сигнал и входные сигналы точно в один и тот же момент времени. Поэтому в случае, когда асинхронный сигнал изменяется вблизи фронта тактового сигнала, существует небольшое временнбе окно, в пределах которого один триггер может воспринять и зафиксировать входной сигнал как 1, а другой - как 0. Противоположные значения сигналов на выходах этих триггеров могут стать причиной неправильной работы системы, одна часть которой будет вести себя так, как если бы входной сигнал был равен 1, а отклик другой части будет таким, как если бы этот сигнал был равен 0. Если сигнал проходит через комбинационную логику, то наличие двух синхронизирующих устройств может не проявиться (рис. 8.93). Из-за различных задержек прохождения сигнала по разным путям в комбинационной логике вероятность появления на выходах триггеров несовместимых результатов только возрастает Это распространенный случай, особенно тогда, когда асинхронные сигналы являются входными сигналами конечного автомата, поскольку две или более переменные состояния, вырабатываемые логикой возбуждения, могут зависеть от значения асинхронного входного сигнала. Правильный способ подачи асинхронного сигнала на вход конечного автомата показан на рис. 8.94. Логика возбуждения видит только один синхронизированный входной сигнал SYNCIN. Комбинационная логика ASYNCIN- (асинхронный входной сигнал) разветвление синхронизирующие устройства SYNC1 CLOCK (системный таетовый сигнал) о Q >CLK >CU< Синхронная система Рис. 8.93. Асинхронный входной сигнал, поступающий на входы двух синхронизирующих устройств после прохождения через комбинационную логику ASYNCIN синхронизирующее устройство SYNCIN (асинхронный входной сигнал) CLOCK - - D Q >OLK (системный тактовый сигнал) Комбинационная логика возбуждения память состояния >CLK D Q >Ci.K - Q1 Рис. 8.94. Асинхронный сигнал на входе конечного автомата, пропущенный через единственное синхронизирующее устройство ООО «Мягкий Дом» - это Отечественный производитель мебели. Наша профильная продукция - это диваны еврокнижка. Каждый диван можем изготовить в соответствии с Вашими пожеланияи (размер, ткань и материал). Осуществляем бесплатную доставку и сборку. Звоните! Ежедневно! (926)274-88-54 Продажа и изготовление мебели. Копирование контента сайта запрещено. Авторские права защищаются адвокатской коллегией г. Москвы. |

|||||||||||||||||||||||||||||