(926)274-88-54

Бесплатная доставка.

Бесплатная сборка.

График работы:

Ежедневно. С 8-00 до 20-00.

Почта: soft_hous@mail.ru

|

Звоните! (926)274-88-54 Бесплатная доставка. Бесплатная сборка. |

Ассортимент тканей График работы: Ежедневно. С 8-00 до 20-00. Почта: soft_hous@mail.ru |

|

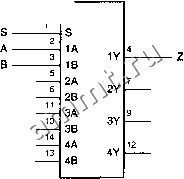

Читальный зал --> Программные средства foundation 1.10. Уровни проектирования цифровых устройств 43 А е- в а- S а- Рис. 1.8. Схема мультиплексора на логических ключах, выполненных по КМОП-технологии Табл. 1.1. Таблица истинности для мультиплексора После того как таблица истинности составлена, согласно традиционным методам логического проектирования, которые будут рассмотрены в параграфе 4.3, мы должны воспользоваться булевой алгеброй и хорошо освоенными алгоритмами минимизации, в результате чего из таблицы истинности получим оптимальное двухуровневое соотношение в терминах И-ИЛИ. В случае мультиплексора у нас получилось бы следующее выражение: Z-SA + SB. Это соотношение читается так: Z равно не S и А или S и В . Продвигаясь еще на один шаг вперед, можно превратить наше соотношение в схему, состоящую из соответствующих вентилей, которая реализует заданную логическую функцию, как показано на рис. 1.9. Если иметь в виду КМОП-технологию, то для четырех вентилей в этой схеме потребуется 14 транзисторов. Рис. 1.9. Логическая схема мультиплексора на уровне вентилей Мультиплексоры применяются очень широко, поэтому в большинстве систем логических элементов имеются готовые структурные блоки, реализующие функцию мультиплексора. Примером может служить микросхема средней степени интеграции 74x157, которая осуществляет переключение входных сигналов, поступающих по двум 4-разрядным шинам. На рис. 1.10 приведено условное обозначение такого устройства; как видим, достаточно изменения одного управляющего бита, чтобы решить проблему одновременного переключения всех сигнальных линий 4-разрядных шин. Рядом с выводами указаньЕ их номера для корпуса DIP с 1 б выводами, в котором находится мультиплексор. 74x157  Рис. 1.10. Условное обозначение мультиплексора, выполненного в виде ИС средней степени интеграции Можно реализовать функцию мультиплексора на части программируемого логического устройства. Языки типа ABEL позволяют с помощью булевых соотношений, подобных приведенному выше, определять выходные сигналы, однако, как правило, для этого удобнее воспользоваться элементами языка более высокого уровня. В табл. 1.2 в качестве примера приведена профамма для мультиплексора на языке ABEL. Первыми тремя сфоками задается имя профамм-ного модуля и тип ПЛУ, на котором должна быть реализована данная функция. В следующих двух строках входам и выходу присваиваются определенные номера выводов ИС. Оператор WHEN служит выражением фактически реализуемой логической функции, которое совсем нетрудно понять, несмофя на то, что язык ABEL вам еще не знаком. Табл. 1.2. Программа для мультиплексора на языке ABEL module chaplmux title Two-input multiplexer example CHAPIMUX device P16V8 A, B, S pm 1, 2, 3; Z pm 13 istype com; equations WHEN S == 0 THEN Z = A; ELSE Z = B; end chaplmux 1.10. Уровни проектирования цифровых устройств 45 На языке VHDL, который является языком более высошго уровня, функцию мультиплексора можно задать более гибко и по иерархическому принципу. Пример программы для мультиплексора на языке VHDL приведен в табл. L3. В первых двух строках указаны стандартная библиотека и набор определений, которые используются в проекте. В следующих четырех строках только определяются входы и выходы проектируемого устройства, и здесь намеренно ничего не говорится о каких-либо деталях того, как именно требуемая функция будет реализована внутри ПЛУ Функциональное поведение устройства конкретизируется в части программы, начинающейся с заголовка architecture . Синтаксис языка VHDL требует небольшого навыка, но оператор when в данной программе выражает собой, по существу, то же самое, что и в варианте программы на языке ABEL. Средства, ответственные за синтез схем, в профаммном пакете языка VHDL могут начинать с этого функционального описания, и результатом их работы будет нужная схема, сформированная в ПЛУ, выполненном по заданной технологии. library IEEE; Программадля use IEEE. std logic 1164. all.- мультиплексора на языке entity Vchaplmux is port ( A, B, S: in STD LOGIC; Z: out STD.LOGIC ); end Vchaplmux; architecture Vchaplmux arch of Vchaplirux is begin Z <= A when S = 0 else B; end Vchaplmux arch; Принудительное разделение определений входов/выходов ( entity ) и внуфен-ней реализации ( architectm-e ) в языке VHDL позволяет разработчику легко задавать альтернативные реализации функций, не внося изменений нигде более в иерархии проекта. Например, в качестве альтернативы можно было бы задать Сфуктурную архитектуру мультиплексора, как это сделано в табл. 1.4. Эта архитектура фактически представляет собой текстовый эквивалент логической схемы, приведенной на рис. L9. ~~~~~~~~~~~~~~~ ~~~~*~~~~~~~~ Табл. 1.4. Струк-architecture Vchaplmux gate arch of Vchaplmux is турная VHDL-npo-signal SN, ASN. SB: STD LOGIC; грамма для мульти- S плексора Ul: INV (S, SN); U2: AND2 (A, SN, ASN); U3: AKD2 (S, B, SB); U4: 0R2 (ASN, SB, Z); end Vchaplmux gate arch; Заглядывая чуть дальше, мы могли бы убедиться в том, что язык VHDL является довольно мощным средством, фактически позволяющим так описать работу про- ООО «Мягкий Дом» - это Отечественный производитель мебели. Наша профильная продукция - это диваны еврокнижка. Каждый диван можем изготовить в соответствии с Вашими пожеланияи (размер, ткань и материал). Осуществляем бесплатную доставку и сборку. Звоните! Ежедневно! (926)274-88-54 Продажа и изготовление мебели. Копирование контента сайта запрещено. Авторские права защищаются адвокатской коллегией г. Москвы. |