(926)274-88-54

Бесплатная доставка.

Бесплатная сборка.

График работы:

Ежедневно. С 8-00 до 20-00.

Почта: soft_hous@mail.ru

|

Звоните! (926)274-88-54 Бесплатная доставка. Бесплатная сборка. |

Ассортимент тканей График работы: Ежедневно. С 8-00 до 20-00. Почта: soft_hous@mail.ru |

|

Читальный зал --> Программные средства foundation Протоколы синхронного доступа в статическое ОЗУ очень полезны в быстродействующих системах. Например, сигналы на адресные входы, на входы управления и на входы данных при записи можно подавать с соблюдением более или менее обычных требований по времени установления и времени удержания относительно системного тактового сигнала, а считываемые данные на выводах памяти с конвейерными выходами доступны в течение почти всего тактового цикла. Очень важно, что разработчик не должен беспокоиться о сложных схемах и о путях прохождения тактового сигнала; в противном случае это было бы необходимо для обеспечения надлежащей работы обычного статического ОЗУ на защелках. Уже в 1999 году выпускались микросхемы памяти типа SSRAM с тактовой частотой до 166 МГц. Заметьте, что среди четырех рассмотренных нами разновидностей памяти типа SSRAM нет единственной лучшей . Лучшей памятью типа SSRAM является та, которая наилучшим образом согласуется с протоколом шины и другими требованиями системы, в которой она используется. 10.4. Динамические оперативные запоминающие устройства Основной ячейкой памяти в статическом ОЗУ является D-защелка, для которой требуются четыре вентиля в дискретном исполнении и от четырех до шести транзисторов в заказном статическом ОЗУ в виде БИС. Дяя того чтобы построить ОЗУ с более высокой плотностью (с ббльшим числом двоичных ячеек в кристалле), разработчики микросхем памяти придумали ячейки, в которых на каждый бит приходится всего лишь по одному транзистору. 10.4.1. Структура динамического ОЗУ Используя только один транзистор нельзя построить элемент с двумя устойчивыми состояниями, в ячейках памяти динамического ОЗУ {dynamic RAM, DRAM) информация сохраняется в виде напряжения на крошечном конденсаторе, доступ к которому осуществляется с помощью МОП-транзистора На рис. 10 31 показана ячейка памяти динамического ОЗУ, в котором запоминается один бит и обращение к которой происходит при подаче на линию слова напряжения высокого уровня. Чтобы запомнить 1, на линию бита подается напряжение высокого уровня, которое через открытый транзистор поступает на конденсатор и заряжает его. Дяя сохранения О на линию бита подается напряжение низкого уровня, в результате чего конденсатор разряжается. линия слова ячейка динамического ОЗУ для хранения 1 бита

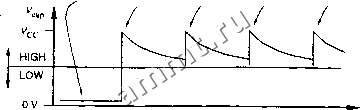

Рис. 10.31. Ячейка памяти в динамическом ОЗУ для хранения одного бита Для чтения информации, хранящейся в ячейке динамического ОЗУ, на линии бита сначала устанавливается напряжение предварительного уровня (precharge voltage), значение которого находится посередине между высоким и низким уровнями, а затем на линию слова подается напряжение высокого уровня. В зависимости от того, заряжен или разряжен конденсатор, напряжение на линии бита становится немного выше или немного ниже предварительного уровня. С помощью усилителя считывания (sense amplifier) это небольшое изменение напряжения обнаруживается и доводится до уровня логической 1 или логического О соответственно. Обратите внимание, что при чтении содержимого ячейки изменяется исходное напряжение на конденсаторе, поэтому после чтения хранившаяся в ячейке информация должна быть снова в нее записана. Емкость конденсатора в ячейке динамического ОЗУ очень мала, но подключенный к конденсатору МОП-транзистор в запертом состоянии имеет очень большое сопротивление. Поэтому требуется относительно большое время (несколько миллисекунд) для того, чтобы конденсатор разрядился настолько, что имевшееся на нем напряжение высокого уровня упало до значения, соответствующего низкому уровню. В течение этого времени конденсатор хранит один бит информации. Естественно, что при работе с компьютером вам было бы не до шуток, если бы приходилось каждые несколько миллисекунд его перезагружать из-за потери информации в его памяти (хотя именно так часто ведет себя операционная система Windows). Поэтому в системах памяти на основе динамических ОЗУ для обновления данных в каждой ячейке предусмотрены периодически повторяющиеся циклы регенерации (refresh cycles). В первых динамических ОЗУ регенерация производилась каждые четыре миллисекунды. Цикл регенерации включает последовательно выполняемые чтение несколью ухудшенного содержимого каждой ячейки в D-защелку и повторную запись полноценного значения логического сигнала из защелки в ячейку. На рис. 10.32 показано напряжение на конденсаторе в ячейке памяти после записи и последующих циклов регенерации. Первые динамические ОЗУ, появившиеся в начале 70-х годов, содержали только 1024 ячейки, а емкость современных динамических ОЗУ достигает 256 мегабитов и больше. Если бы требовалось обновлять все ячейки по очереди каждые четыре миллисекунды, то у вас возникли бы проблемы: время, отводимое на регенерацию содержимого одной ячейки, было бы гораздо меньше 1 НС, и не оставалось бы никакого времени для выполнения полезных операций чтения и записи. К счастью, как будет показано позже, динамические ОЗУ организованы в виде двухмерных матриц и за одну операцию регенерируется целая строка матрицы. У первых динамических ОЗУ было 256 строк, и требовалось 256 циклов регенерации каждые четыре миллисекунды, то есть цикл регенерации очередной строки должен был выполняться примерно через каждые 15.6 МКС. Современные матрицы памяти состоят из 4096 строк и их содержимое необходимо обновлять только один раз за 64 мс, так что по-прежнему цикл регенерации очередной строки должен производиться каждые 15.6 мкс. В типичном случае длительность цикла регенерации составляет менее 100 не, так что динамическое ОЗУ доступно для полезных операций чтения и записи в . сезедие 4рлее чем .99 времени..  время Рис. 10.32. Напряжение на конденсаторе в ячейке динамического ОЗУ после записи и выполнения циклов регенерации (HIGH - высокий уровень, LOW - низкий уровень) На рис. 10.33 приведена внутренняя структура динамического ОЗУ 64Кх1. Емкость логической матрицы составляет 64Кх1 битов, но физически матрица представляет собой квадрат, состоящий из 256x256 ячеек. Несмотря на то, что память содержит 64К ячеек, микросхема имеет только восемь мультиплексированных адресных входов (multiplexed address inputs). Полный 16-разрядный адрес поступает в микросхему за два шага по двум сигналам управления: по стробу адреса строки RASJ- (row address strobe) и по стробу адреса столбца CAS L (column address strobe). Благодаря мультиплексированию адресных входов удается сократить число выводов, что важно для компактной реализации запоминающих устройств, и, кроме того, мультиплексирование совершенно естественным образом согласуется с двухсупенчатыми методами доступа к динамическому ОЗУ, которые вскоре будут описаны.

матрица 256 х 256 адрес строкич., RAS L CAS L WE L адрес столбца управля устройство управление защелками, мультиплексором и демультип-лексором защелки столбцов, мультиплексор и демультиплексор DOUT Рис. 10.33. BHVTPeHHmCTDVKTVOa пиняммиоппгг. n-V fi/lk-v1 хранится О , записана 1 регенерация регенерация регенерация ООО «Мягкий Дом» - это Отечественный производитель мебели. Наша профильная продукция - это диваны еврокнижка. Каждый диван можем изготовить в соответствии с Вашими пожеланияи (размер, ткань и материал). Осуществляем бесплатную доставку и сборку. Звоните! Ежедневно! (926)274-88-54 Продажа и изготовление мебели. Копирование контента сайта запрещено. Авторские права защищаются адвокатской коллегией г. Москвы. |