(926)274-88-54

Бесплатная доставка.

Бесплатная сборка.

График работы:

Ежедневно. С 8-00 до 20-00.

Почта: soft_hous@mail.ru

|

Звоните! (926)274-88-54 Бесплатная доставка. Бесплатная сборка. |

Ассортимент тканей График работы: Ежедневно. С 8-00 до 20-00. Почта: soft_hous@mail.ru |

|

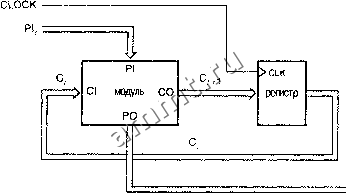

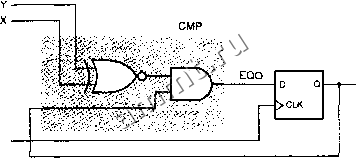

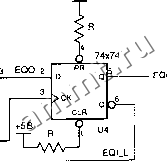

Читальный зал --> Программные средства foundation Табл. 8.34. VHDL-программа для модифицированного генератора шестифазных колебаний library IEEE; use IEEE.st<i logic n64,all; tsiitlty VtiBJeg12 is port ( MCLK, RESET, RUN, REST4P.T; in STD.LOGIC; - clock, courrsl inputs P L: otit STD ..LOGIC.VECTOR (1 to 6) - ar,tiv -loM phase ciutpats end VtiHeg12; architecture Vt3.3segi2 arch of Vtiffi6gl2 is issgnal IP, .техТР: STD.LOGIC.VECTOR (1 to 6); - latern?.: active-isigh paase aiguals begin process ( MCLK, IP, MEXTP) variable ТЕИР: STD.LOCJC.VECTOR <1 to 6); - temporary for signal shift coistant IDLE: STD.LOGIC./ECTOR С to 6) ;= С0 , 0,0, 0,0 constant FIRSTP: STD.LDSIC.W.CTOR С to 6) { 1,0,0 ,0, 0,0) ; begin it (над-event and HCL.K i) then if (RESET=l) then IP IDLE; ЖХТР <= IDLE; slsif (aESTART-l) or (IP-IDLE and NEXTPIDLE) then IP <= IDLE; ЛЕХТР FIRSTP; elsif (НГО1=Г) then if {IP-IDLE) and (HEXTP-ISLE) ther, NEXT? <= FiRSTP; e:.se TElP := IP; IP <> HEXTP; KEXTP <= ГЕКР(6) к tEKP(l to S) ; end if; end if; end if; P.L <= no-. IP; end process; rd Vtisegi.arch; Как и в предыдущей профамме, в теле архитектуры объявлен б-разрядный сигнал IPC высоким активным уровнем, который используется для чтения и записи и становится в конце концов выходным сигналом устройства P L с низким активным уровнем. Добавочный 6-разрядный сигнал NEXTP хранит остающиеся 6 двоичных переменных состояния. Константы IDLE и FIRSTP делают профамму более удобочитаемой. Заметьте, что 6-разрядная переменная TEMP используется только как место временного хранения старого значения IP при осуществлении сдвига: в IP загружается содержимое NEXTP, а в NEXT? - сдвинутое старое значение IP. Поскольку операторы присваивания в процессе выполняются последовательно, мы не могли бы обойтись простой записью 1Р<= NEXTP; NEXTP<= IP (6) &IP (1 to 5) ; . Если бы мы так сделали, то в NEXTP попало бы новое значение IР, а не старое. Обратите также внимание на следующее: так как TEMP является локальной переменной, а не сигналом, ее значение вне процесса не видно. Кроме того, при очередном обращении к процессу никогда не используется значение TEMP, образовавшееся при предыдущем вызове процесса. Поэтому VHDL-компилято-ру не нужно синтезировать никаких триггеров для хранения значения TEMP.  Рис. 8.74. Общая структура последовательностной схемы, эквивалентной итерационной схеме Поскольку итерационная схема является комбинационной, все ее первичные и фаничные входные сигналы можно подать одновременно, а все ее первичные и граничные выходные сигналы доступны спустя время, равное комбинационной задержке. В последовательностной схеме первичные входные сигналы должны поступать последовательно, по одному комплекту на каждом такте, и первичные выходные сигналы должны вырабатываться в соответствующие моменты времени. Поэтому входные сигналы часто формируют с помошью регистров сдвига с последовательным выводом, а выходные сигналы собирают в регистрах сдвига с последовательным вводом. По этой причине часто говорят, что в последовательностной схеме состояния итерационной схемы поочередно следуют одно за другим. *8.6. Итерационные и последовательностные схемы с итерационными схемами мы познакомились в разделе 5.9.2. Функцию итерационной схемы, состоящей из и модулей, может выполнить последовательностная схема, в которой модуль имеется лишь в одном экземпляре, но ей требуется совершить п шагов (за п тактов), чтобы получить нужный результат Это блестящий пример пространственно-временного обмена при цифровом проектировании. Как видно из рис. 8.74, в последовательностной схе.ме для сохранения значений сигналов в межкаскадном соединении в конце каждого шага используются триггеры; именно их выходные сигналы служат входными сигналами межкаскадного соединения в начале следующего шага. Перед началом первого такта триггеры необходимо загрузить граничными значениями входных сигналов; по окончании и-го такта они содержат фаничные значения выходных сигналов. CLOCK  Рис. 8.75. Упрощенная схема последовательного компаратора +5 в RESET L CLOCK 74x86 ЦТ-Хз 1 ,.,Г 74X00  Рис. 8.76. Уточненная схема последовательного компаратора С помощью последовательного компаратора -разрядное сравнение осуществляется за и + 1 тактов. Сигнал RESET L действует на первом такте, а на следующих п тактах этот сигнал имеет неактивный уровень, и на входы X и Y подаются биты данных. На выходе EQI вырабатывается результат сравнения, удерживаемый в течение периода, следующего за очередным перепадом в тактовом сигнале. На рис. 8.77 приведены временные диафаммы для последовательного сравнения в 4-х разрядах. Паразитные импульсы в сигнале EQO возникают в те моменты времени, когда изменяются сигналы на выходах комбинационных схем в качестве отклика на поступление новых значений сигналов на входы X и Y. На рис. 8.75 в качестве примера приведена основная схема последовательного компаратора {serial comparator). Затененный участок схемы тождественен одному модулю итерационного компаратора, изображенного на рис. 5.80 Более подробная схема показана на рис. 8.76 в предположении, что компаратор собирается на основе ИС малой степени интефации. В схеме предусмотрен синхронный сброс: при подаче сигнала на этот вход между каскадный триггер на следующем такте устанавливается в начальное единичное состояние. Это начальное значение соответствует граничному входному сигналу итерационного компаратора. ООО «Мягкий Дом» - это Отечественный производитель мебели. Наша профильная продукция - это диваны еврокнижка. Каждый диван можем изготовить в соответствии с Вашими пожеланияи (размер, ткань и материал). Осуществляем бесплатную доставку и сборку. Звоните! Ежедневно! (926)274-88-54 Продажа и изготовление мебели. Копирование контента сайта запрещено. Авторские права защищаются адвокатской коллегией г. Москвы. |