(926)274-88-54

Бесплатная доставка.

Бесплатная сборка.

График работы:

Ежедневно. С 8-00 до 20-00.

Почта: soft_hous@mail.ru

|

Звоните! (926)274-88-54 Бесплатная доставка. Бесплатная сборка. |

Ассортимент тканей График работы: Ежедневно. С 8-00 до 20-00. Почта: soft_hous@mail.ru |

|

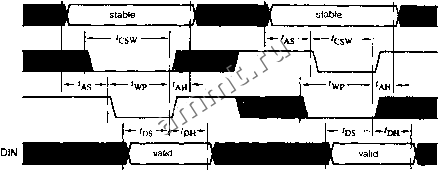

Читальный зал --> Программные средства foundation 10.3.3. Временные параметры статического ОЗУ На рис. 10.22 приведены временные диафаммы и определение временнь/х параметров, которые обычно задаются для операции чтения из статического ОЗУ: I Время доступа по шине адреса {access time from address). Этим параметром определяется время, спустя которое выходные данные принимают установившееся значение после изменения адреса при условии, что сигналы ОЕ и CS к этому времени уже имеют активный уровень или достаточно скоро должны стать такими. Когда разработчики говорят о 70-наносекунд-ном статическом ОЗУ, обычно они имеют в виду этот параметр. Время доступа по входу выбора кристалла {access time from chip select) Этим параметром определяется время, спустя которое выходные данные принимают установившиеся значения после перехода сигнала CS на активный уровень при условии, что сигналы на адресных входах и сигнал ОЕ уже имеют активный уровень или достаточно скоро должны стать такими. Часто значение этого параметра совпадает с временем t, но иногда его величина больше при работе статического ОЗУ в режиме пониженного потребления мощности и меньше t, когда статическое ОЗУ не находится в этом режиме. Время разрешения выхода {output-enable time). Этим параметром определяется время, через которое буферы с тремя состояниями на выходе выйдут из высокоомного состояния, после того как оба сигнала ОЕ и CS перейдут на активный уровень. Этот параметр обычно меньше, чем величина t, поэтому внутри ОЗУ вызов данных возможен раньше, чем сигнал ОЕ примет активное значение; во многих приложениях это свойство используется для достижения малых времен доступа, чтобы избежать борьбы в шине . Время запрещения выхода {output-disable time). Этим параметром определяется время, необходимое для того, чтобы буферы с тремя состояниями на выходе перешли в высокоомное состояние, после того как сигналы OE L или CS L перейдут на неактивный уровень. Время удержания сигнала на выходе {output-hold time). Этот параметр показывает, как долго выходные данные сохраняют установившиеся значения после изменения адреса на входе. ADDR CS L OE L DOUT Stable valid stable valid Заметьте, что WE L= HIGH stable Рис. 10.22. Временные параметры для операции чтения из статического ОЗУ (stable - установившиеся значения; valid - достоверные данные) Вы могли заметить, если обратили внимание, что временнь/е диаграммы и временнь/е параметры для режима чтения из статического ОЗУ идентичны с теми, которые были введены при рассмотрении режима чтения из ПЗУ в разделе 10.1.5. Это именно так: когда не производится запись в статическое ОЗУ, его можно использовать точно так же, как ПЗУ. Позже мы увидим, что совсем иначе обстоит дело с динамическими ОЗУ. Временные параметры операции записи, указанные на рис. 10.23, определяются следующим образом: Время установления адреса до начала записи (address setup time before write). Сигналы на всех адресньгх входах должны оставаться постоянными в течение указанного времени перед тем, как оба сигнала CS и WE примут активное значение. В противном случае данные могут быть искажены и нельзя сказать, в каких именно ячейках это может произойти. АН Время удержания адреса после окончания записи (address hold time after write). Так же, как и в отношении параметра t, сигналы на всех адресных входах должны поддерживаться неизменными в течение времени после того как хотя бы один из сигналов CS или WE перейдет на неактивный уровень. csw Время установления сигнала выбор кристалла)) до окончания записи (chip-select setup time before end of write). Уровень сигнала CS должен оставаться активным в течение отрезка времени длительностью не менее t перед окончанием цикла записи. Длительность импульса записи (write-pulse width). Для надежного запоминания данных в выбранной ячейке сигнал WE должен иметь активный уровень в течение времени, равного, по крайней мере, f. ds Время установления данных до окончания записи (data setup time before end of write). Сигналы на всех входах данных должны иметь постоянные значения в течение этого отрезка времени перед окончанием цикла записи. В противном случае данные могут оказаться незапомненными. dh Время удержания данных после окончания записи (data hold time after end of write). Аналогично параметру t, сигналы на всех входах данных должны поддерживаться неизменными в течение этого интервала времени после окончания цикла записи. Производителями статических ОЗУ определяются два типа цикла записи: запись по сигналу WE (WE-controlled write) и запись по сигналу CS (CS-controlled write), как показано на рисунке. Единственное различие между этими циклами состоит в том, какой из сигналов WE или CS последним переходит на активный уровень и у какого из этих сигналов первым уровень становится неактивным при разрешении операции записи внутри статического ОЗУ. Требования к временным параметрам при записи в статическое ОЗУ можно было бы несколько ослабить, если бы в ячейках вместо защелок применялись переключающиеся по фронту D-триггеры с объединенными тактовым входом и входом разрешения, на которые подавались бы сигналы SEL и WR. Однако так не поступают, потому что при этом по меньшей мере вдвое увеличилась бы пло- ADDR CS L WE L (запись по.сипвпу WE) (з 1ись по ситалу CS)  Рис. 10.23. Временные параметры для операции записи в статическое ОЗУ (stable - установившиеся значения; valid - достоверные данные) Физические размеры матрицы в кристалле большого статического ОЗУ напрямую не связаны с емкостью памяти. Как и в ПЗУ, ячейки статического ОЗУ образуют почти квадратную матрицу, и при чтении внутри ОЗУ считывается полная строка. Например, структура микросхемы статического ОЗУ емкостью 32Кх8 может быть очень похожа на структуру ПЗУ 32Кх8, приведенную на рис. 10.9. Во время чтения требуемые данные проходят на выходную шину данных через мультиплексоры столбцов в соответствии с подмножеством значений адреса в определенных разрядах (в примере с ПЗУ такими разрядами являются А5-А0). Схема разрешения записи обеспечивает доступ при записи только к одному столбцу в каждом подмасси-ве, который определяется тем же самым подмножеством адресных битов. 10.3.4. Стандартные статические ОЗУ в настоящее время выпускаются статические ОЗУ различной емкости и с разным быстродействием. В 1999 году самые большие обычные статические ОЗУ, выполненные по КМОП-технологии имели организацию 256Кх16 (256К 16-разрядных слов), 512Кх8 или 1Мх4 (4 Мбит) и время доступа 10 не. Самые быстрые ТТЛ/ КМОП-совместимые статические ОЗУ, также выполненные по КМОП-технологии, содержали всего лишь 1 Кх4 ячеек памяти (4 Кбита), но имели время доступа 2.7 не! Среди производителей статических ОЗУ нет согласия в отношении обозначения микросхем, хотя сами ИС часто имеют одинаковую цоколевку и взаимозаменяемы. На рис. 10.24 приведены обозначения и цоколевка статических ОЗУ фирмы Hitachi емкостью от 8Кх8 до 512Кх8. Эти микросхемы удобны для применения в лабораторном проектировании: им требуется напряжение питания 5 В и размещаются они в DlP-Kopnycax. Эти же статические ОЗУ имеются также и в более ком- щадь, занимаемая каждой ячейкой в кристалле, так как D-триггер состоит из двух защелок. Таким образом, разработчику логических устройств приходится согласовывать временные параметры статических ОЗУ на защелках с временными параметрами переключающихся фронту регистров и с временными требованиями конечных автоматов, используемых в системе. ООО «Мягкий Дом» - это Отечественный производитель мебели. Наша профильная продукция - это диваны еврокнижка. Каждый диван можем изготовить в соответствии с Вашими пожеланияи (размер, ткань и материал). Осуществляем бесплатную доставку и сборку. Звоните! Ежедневно! (926)274-88-54 Продажа и изготовление мебели. Копирование контента сайта запрещено. Авторские права защищаются адвокатской коллегией г. Москвы. |