(926)274-88-54

Бесплатная доставка.

Бесплатная сборка.

График работы:

Ежедневно. С 8-00 до 20-00.

Почта: soft_hous@mail.ru

|

Звоните! (926)274-88-54 Бесплатная доставка. Бесплатная сборка. |

Ассортимент тканей График работы: Ежедневно. С 8-00 до 20-00. Почта: soft_hous@mail.ru |

|

Читальный зал --> Программные средства foundation R L[7 0]. R LO 4 74LS148 74LS138 R L1 3 R L2 2. R L3 1. R L4 13 . R L5 12 . R L6 11 , R L7 10 15 14 13 12 11 Ю 74LS04 R LO 1 R-L1 3. R-U2 5, D> R l-3 t> R L4 R-L5 13, R L6 R-L7 3, AO О A1 О A2 !> GS О EO :> .9 AO A[2 01 AVALID D L[0 7]

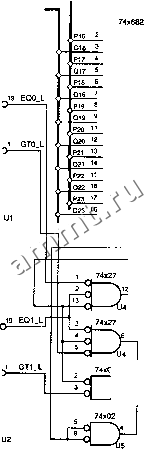

74LS00 D L0 D L1 U4 <5. D L2 10 U4 Ф-10 D L3 13 D L4 D L5 3 RD L0 6 RD L1 e RD U2 RD L3 U6 L 3 RD.Uf 6 RD L5 U5 6 D L6 10 L> I- U7 e RD Le D L7 13 I-у U7 RD L7  74LS148 О IB ol5 14 13 12 11 10 AO Al A2 GS О EO O 9 BO 7 B1 .A[2 0 AVALID . B[2 0] BVALID Рис. 6.6. Схема шифратора, обнаруживающего запросы с первым и вторым по старшинству приоритетами 6.1.4. Расширение компараторов в разделе 5.9.4 мы показали, как можно строить большие компараторы путем каскадного включения 4-разрядных компараторов 74x85. Поскольку ИС 74x85 предусматривают их последовательное включение, на основе этих микросхем можно создавать сколь угодно большие компараторы. У 8-разрядного компаратора 74x682 вообще нет никаких входов и выходов для каскадного включения. Поэтому может показаться, на первый взгляд, что этой ИС нельзя воспользоваться для построения больших компараторов. Но это Не тяк- Если вы задумаетесь о сущности сравнения многоразрядных слов, то станет ясно, что два многоразрядных операнда - скажем, по 32 бита (по четыре байта) в каждом - равны только в том случае, когда равны их соответствующие байты. Если при сравнении необходимо принимать решение вида больше чем или меньше чем , то результат сравнения определяется по самым старшим из неравньгх байтов. Реализацией этих идей служит схема (рис. 6.7), позволяющая обнаруживать равенство двух 24-разрядных операндов или выносить решение вида больше чем с помощью трех 8-разрядных компараторов 74x682. Сравнение 24-разрядных операндов осуществляется на основе результатов сравнения отдельных 8-разрядных слов; выходные сигналы формируются дополнительной комбинационной схемой согласно следующим равенствам: PEQQ = eq2 eq1 EQO PGTQ = gt2 + eq2 gt1 + eq2 eq1 СТО. [23 01 I Р[23 0] Q[23 0] 74x682

74x682

д19 EQ2 L -PEQQ 2 74X27 Рис. 6.7. Схема 24-разрядного компаратора не следуйте слепо за рекламой! Расточительность исходного варианта, представленного на рис. 6.8(a), возможно, была очевидна для вас с самого начала, но он демонстрирует важный принцип проектирования на основе стандартных блоков: Для обработки данных используйте стандартные блоки и ищите способ заставить одни и те же блоки в разное время выполнять различные функции или работать в различных режимах. По мере надобности создавайте схемы управления для выбора соответствующих функций, чтобы уменьшить общее число компонентов в устройстве. Как впечатляюще показано на рис. 6.8(c), этот подход позволяет сэкономить много корпусов. При проектировании на основе интегральных микросхем не следует поддаваться рекламе: У нас есть все, что вам нужно, и даже больше ! Такой параллельный подход к расширению компаратора в действительности дает большее быстродействие, нежели последовательное включение ИС 74x85, потому что исключается задержка распространения сигналов в каждом каскаде по пути от входов до выходов, с помощью которых компараторы соединяются один за другим. Параллельный подход и двухуровневая логика И-ИЛИ для объединения результатов сравнения 8-разрядных слов позволяют создавать компараторы с очень большим числом входов, которое ограничено только коэффициентом объединения по входу схем в логике И-ИЛИ. Применяя для объединения дополнительные логические схемы, можно строить сколь угодно большие компараторы. 6.1.5. Компаратор с управляемым режимом работы Довольно часто требования, предъявляемые к цифровой схеме делают очевидным решение поставленной задачи на основе ИС средней степени интефации или других стандартных блоков. Рассмотрим, например, такую задачу. Построить комбинационную схему, на входы которой подаются два 8-разрядных целых двоичных числа без знакаХиУи сигнал управления MIN/MAX, а на выходе возникает 8-разрядное целое двоичное число без знака Z, такое что Z = min(X,Y), если MIN/MAX = 1, и Z = тах(Х, У), если MIN/MAX = 0. Нетрудно представить себе эту схему составленной из ИС средней степени интефации. Очевидно, что для определения, какое из чисел X илиУбольше, можно воспользоваться компаратором. Сигнал с выхода компаратора может управлять мультиплексорами, на выходах которых будут вырабатываться сигналы min(X, У) и тах(Х, У), а с помощью другого мультиплексора можно выбрать один из этих результатов в зависимости от значения сигнала MIN/MAX. Блок-схема устройства, в котором реализован этот подход, приведена на рис. 6.8(a). ООО «Мягкий Дом» - это Отечественный производитель мебели. Наша профильная продукция - это диваны еврокнижка. Каждый диван можем изготовить в соответствии с Вашими пожеланияи (размер, ткань и материал). Осуществляем бесплатную доставку и сборку. Звоните! Ежедневно! (926)274-88-54 Продажа и изготовление мебели. Копирование контента сайта запрещено. Авторские права защищаются адвокатской коллегией г. Москвы. |