(926)274-88-54

Бесплатная доставка.

Бесплатная сборка.

График работы:

Ежедневно. С 8-00 до 20-00.

Почта: soft_hous@mail.ru

|

Звоните! (926)274-88-54 Бесплатная доставка. Бесплатная сборка. |

Ассортимент тканей График работы: Ежедневно. С 8-00 до 20-00. Почта: soft_hous@mail.ru |

|

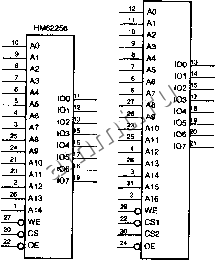

Читальный зал --> Программные средства foundation HM62ei28 НМ628512 НМ6264

.22. 2в.

Рис. 10.24. Условные обозначения стандартных статических ОЗУ в DIP-кор-пусах с 28 и 32 выводами Первые два статических ОЗУ, приведенные на рисунке, размещены в DIP-кор-пусах с 28 выводами и имеют такую же цоколевку, как и программируемые ПЗУ с тем же объемом памяти (рис. 10.11). Микросхема НМ6264 емкостью 8Кх8 подобна EPROM 2764 за исключением того, что у нее имеется вход разрешения записи и два входа выбора кристалла, а не один; для того чтобы микросхема была переведена в активный режим, оба сигнала CS1 L и CS2 должны перейти на активный уровень. Микросхема НМ62256 емкостью 32Кх8 подобна EPROM 27256 с добавлением входа разрешения записи. Обе микросхемы поставляются многими производителями, хотя часто имеют разные обозначения; время доступа у этих микросхем находится в диапазоне от 15 не до 150 не. Последние два статических ОЗУ, показанных на рисунке, выполнены в корпусах DIP с 32 выводами. Емкость ИС НМ628128 составляет 128Кх8, а ИС НМ628512 - 512Кх8. Статические ОЗУ, приведенные нарис. 10.24, имеют двунаправленные шины данных: для чтения и для записи используются одни и те же выводы данных. Это требует незначительного изменения внутренней логики управления, как показано на рис. 10.25. Каждый буфер автоматически запирается (переходит в высокоомное состояние) всякий раз, когда сигнал WE L принимает активное значение, даже в том случае, когда активный уровень имеет сигнал OE L Однако временные параметры и требования для операций чтения и записи практически тождественны тем, какие бьши приведены в предыдущем разделе. пактных корпусах, а в последнее время они обычно поставляются только в компактных корпусах и работают с более низкими напряжениями питания, равным 3.3 В или 2.5 В. 992 Глава 10. Память и микросхемы типа CPLD и FPGA WE L-CS L - OE L > - IN { Wfl IN OUT IN OUT SfcL SEL <3(WR DI03 Dloa D101 0100 Рис. 10.25. Управление выходными буферами в статическом ОЗУ с двунаправленной шиной данных Обычно статические ОЗУ используют для хранения данных в небольших микропроцессорных системах и часто они встречаются во встроенных цифровых системах (в телефонах, тостерах, стабилизаторах напряжения и тд.). В универсальных вычислительных машинах чаще применяются рассматриваемые в параграфе 10.4 динамические ОЗУ (DRAM), поскольку у них выше плотность размещения ячеек памяти и меньше стоимость в расчете на один бит Очень быстрые статические ОЗУ часто используются в высокопроизводительных компьютерах в качестве кэш-памяти для сохранения многократно используемых команд и данных. Фактически, необходимость в высоком быстродействии кэшпамяти в персональном компьютере привела к разработке и широкому распространению сверхбыстрого, тактируемого интерфейса SRAM. Рассмотренные в этом разделе стандартные статические ОЗУ мы будем теперь называть асинхронными статическими ОЗУ (asynchronous SRAM), чтобы отличать их от нового типа памяти, рассматриваемого ниже. * 10.3.5. Синхронные статические ОЗУ Внутри новой разновидности статических ОЗУ, называемых синхронными статическими ОЗУ (synchronous SRAM, SSRAM), по-прежнему применяются защелки, но имеется тактируемый интерфейс для сигналов управления, адресных сигналов и сигналов данных. Как показано на рис. 10.26, на пути адресных сигналов и сигналов управления находятся внутренние переключающиеся по фронту регистры AREG и CREG. В результате действие, задаваемое перед нарастающим фронтом тактового сигнала, выполняется внутри микросхемы наследующем такте. При записи в регистре INREG фиксируются входные данные. Если выходы микросхемы конвейерные , то в ней имеется регистр OUTREG, обеспечивающий сохранение данных, выводимых при чтении; в случае сквозных выходов регистр OUTREG отсутствует. Первыми появились SSRAM с задержанной записью и сквозными выходами (late-write SSRAM with flow-through outputs). При выполнении операции чтения, показанной нарис. 10.27(a), выборка сигналов на входах управления и адресных входах производится на нарастающем фронте тактового сигнала, а внутренний регистр адреса AREG загружается только при условии, что сигнал ADS L имеет активный уровень. В течение следующего такта происходит обращение к внутренней матрице статического ОЗУ, и считываемые данные поступают на выводы шины данных DIO устройства. Возможен также пакетный режим работы такой памяти. 10.3. Статические оперативные запоминающие устройства 993 при котором данные читаются из следующих одна за другой ячеек. В этом режиме регистр AREG ведет себя как счетчик, так что нет необходимости в каждом цикле подавать новый адрес. (Управляющие сигналы, которые поддерживают пакетный режим, на рис. 10.26 и 10.27 не показаны.) AREG мвгфица статического ADDR : ADS L CLK CS GW L -O CE -> GREG лоп4ка управления - > INREG > ADDRESS CS WE DOUT Ж>1 OUTREG только в устройствах с конвейерными выходами Рис. 10.26. Внутренняя структура синхронного статического ОЗУ В цикле записи, изображенном нарис. 10.27(b), записываемые данные выбираются спустя один такт после зафузки регистра адреса и временно хранятся во внутреннем регистре INREG. Поэтому по крайней мере на один такт после загрузки адреса должна быть задержана подача сигнала ADS L, чтобы при выполнении записи адрес в регистре AREG оставался неизменным. Запись происходит в течение такта, следующего за фронтом, по которому управляющий сигнал записи GW L ( global write ) переходит на активный уровень. Как и при чтении, возможен пакетный режим, когда запись по последовательным адресам осуществляет- ООО «Мягкий Дом» - это Отечественный производитель мебели. Наша профильная продукция - это диваны еврокнижка. Каждый диван можем изготовить в соответствии с Вашими пожеланияи (размер, ткань и материал). Осуществляем бесплатную доставку и сборку. Звоните! Ежедневно! (926)274-88-54 Продажа и изготовление мебели. Копирование контента сайта запрещено. Авторские права защищаются адвокатской коллегией г. Москвы. |