(926)274-88-54

Бесплатная доставка.

Бесплатная сборка.

График работы:

Ежедневно. С 8-00 до 20-00.

Почта: soft_hous@mail.ru

|

Звоните! (926)274-88-54 Бесплатная доставка. Бесплатная сборка. |

Ассортимент тканей График работы: Ежедневно. С 8-00 до 20-00. Почта: soft_hous@mail.ru |

|

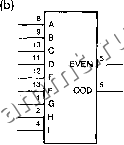

Читальный зал --> Программные средства foundation Рис. 5.72. Условные обозначения: (а) схемы ИСКЛЮЧАЮЩЕЕ ИЛИ; (Ь) схемы ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ На рис. 5.73 приведена цоколевка МИС 74x86 с 14 выводами, в одном корпусе которой размещаются четьфе схемы ИСКЛЮЧАЮЩЕЕ ИЛИ. Новые семейства МИС не содержат схем ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ, хотя их легко реализовать в FPGA; они имеются также в библиотеках специализированных ИС и в виде примитивов в языках описания схем. 1 \ т-9 \ т---Рис. 5.73. Цоколевка микросхемы 2 I ) 10 ]) > 74x86, содержащей четыре 2-вхо-72-- 71 довых вентиля ИСКЛЮЧАЮЩЕЕ 5.8.2. Схемы проверки на четность Если включить последовательно п схем ИСКЛЮЧАЮЩЕЕ ИЛИ так, как показано на рис. 5.74 (а), то получится схема ИСКЛЮЧАЮЩЕЕ ИЛИ с и +1 входами и одним выходом. Такую схему называют схемой проверки на нечетность {odd-parity circuit), потому что сигнал на ее выходе равен 1, если единицы присутствуют на нечетном числе ее входов. Схема, приведенная нарис. 5.74(b), также осуществляет проверку на нечетность, но является более быстродействующей, поскольку в ней вентили образуют древовидную структуру. Если инвертировать выход любой из представленных схем, то получим схему проверки на четность {even-parity circuit), у которой выходной сигнал равен 1, если на четном числе входов имеются единицы. 5.8.3. 9-разрядная микросхема проверки на четность 74x280 Вместо того, чтобы создавать многоразрядную схему проверки на четность с помощью отдельных схем ИСКЛЮЧАЮЩЕЕ ИЛИ, выгоднее разместить все вентили ИСКЛЮЧАЮЩЕЕ ИЛИ в одном корпусе СИС, у которой с внещними выводами соединены только первичные входы и выход. Таким устройством является изображенная на рис. 5.75 9-разрядная схема проверки на четность 74x280. У нее девять входов и два выхода, которые указывают на наличие четного или нечетного числа единиц на входах. 12 13 !4 Рис. 5.74. Каскадное включение схем ИСКЛЮЧАЮЩЕЕ ИЛИ: (а) соединение с последовательным опросом, (Ь) древовидная структура 74x280 (11) (12) (13)  EVEN Уж> Рис. 5.75.9-разрядная схема проверки на четность/нечетность 74x280. (а) принципиальная схема и цоколевка для стандартного корпуса DIP с 16 выводами, (Ь) традиционное условное обозначение (EVEN - четное число единиц на входах, ODD - нечетное число единиц на входах) ПОВЫШЕНИЕ БЫСТРОДЕЙСТВИЯ ДРЕВОВИДНОЙ СХЕМЫ ИСКЛЮЧАЮЩЕЕ ИЛИ Если бы каждый из вентилей ИСКЛЮЧАЮЩЕЕ ИЛИ нарис. 5.75 был составлен из отдельных схем И-НЕ, как показано нарис. 5.71(b), то ИС 74x280 была бы значительно медленнее: задержка распространения сигнала в ней была бы эквивалентна4 -3 + 1 = 13 задержкам одного вентиля И-НЕ. Поэтому типичное исполнение ИС 74x280 основано на применении структуры И-ИЛИ-НЕ с 4 выводами. Именно такой структурой реализуется функция, выполняемая каждой парой схем ИСКЛЮЧАЮЩЕЕ ИЛИ, объединенных на рисунке одним затененным прямоугольником; при этом задержка примерно равна задержке одного вентиля И-НЕ. На входах А-1 помещены буферы, состоящие из двух инверторов, для того чтобы каждый из входов представлял собой одиночную нагрузку для схемы, с выхода которой поступает сигнал. Результирующая задержка распространения у выполненной таким образом схемы 74x280 составляет 5, а не 13 задержек одной инвертирующей схемы. 5.8.4. Применение схем проверки на четность в параграфе 2.15 мы описали коды для обнаружения ошибок, возникающих при передаче и хранении данных, в которых используется дополнительный бит, называемый битом четности. В коде с проверкой на четность бит четности выбирают так, чтобы общее число единичных битов в кодовом слове было четно. Схемы проверки на четность, аналогичные 74x280, применяются как для формирования нужного значения бита четности при хранении или передаче кодового слова, так и для проверки на четность при считывании кодового слова из памяти или при его приеме. На рис. 5.76 показано, как можно применять схему проверки на четность для обнаружения ошибок в памяти микропроцессорной системы. Память хранит 8-разрядные байты плюс бит четности для каждого байта. Для передачи данных в память и для извлечения данных из нее микропроцессор использует двунаправленную шину D[0:7]. Кроме того, имеются две линии управления RD и WR для задания желаемой операции -чтения или записи - и вырабатывается сигнал ERROR, указывающий на наличие ошибки при проверке на четность при чтении. Другие детали, касающиеся микросхем памяти (адресные входы и др.), на рисунке опущены; подробнее микросхемы памяти описаны в главе 10. При рассмотрении проверки на четность нас интересуют только линии передачи данных в память и из нее. Для сохранения байта в микросхеме памяти мы задаем адрес (не показанный на рисунке), размещаем на шине D[0-7] запоминаемый байт и подаем сигнал записи WR: на вход PIN при этом поступает сформированный бит четности. Вентиль И, предшествующий входу I микросхемы 74x280, обеспечивает постоянное присутствие на этом входе О, кроме интервалов времени, в течение которых выполняется операция чтения; благодаря этому во время записи сигнал на выходе микросхемы 280 зависит только от четности данных на шине D. Со входом PIN соединен выход ODD микросхемы 280, поэтому общее число запоминаемых единиц оказывается четным. ООО «Мягкий Дом» - это Отечественный производитель мебели. Наша профильная продукция - это диваны еврокнижка. Каждый диван можем изготовить в соответствии с Вашими пожеланияи (размер, ткань и материал). Осуществляем бесплатную доставку и сборку. Звоните! Ежедневно! (926)274-88-54 Продажа и изготовление мебели. Копирование контента сайта запрещено. Авторские права защищаются адвокатской коллегией г. Москвы. |