(926)274-88-54

Бесплатная доставка.

Бесплатная сборка.

График работы:

Ежедневно. С 8-00 до 20-00.

Почта: soft_hous@mail.ru

|

Звоните! (926)274-88-54 Бесплатная доставка. Бесплатная сборка. |

Ассортимент тканей График работы: Ежедневно. С 8-00 до 20-00. Почта: soft_hous@mail.ru |

|

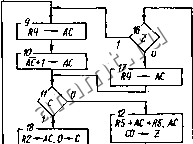

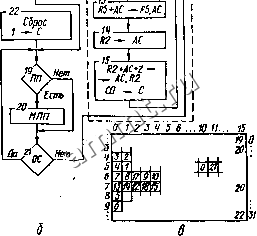

Читальный зал --> Особенности интегральных микросхем могут оказывать МК условного перехода, например, IFL. В этом случав формирование адреса (t-f- 1)-й МК следует задержать на один такт, что можно реализовать как аппаратно, так и программно. При аппаратной реализации в поле МК выделяется разряд, который управляет подачей синхронизирующего сигнала в ЦПЭ (рис. 1.31, б). Наличие 1 в указанном разряде запрещает поступление спадов S, по которым фиксируется информация в регистрах ДЯ5. Вследствие этого создается возможность просмотра результатов выполнения МК без перемещеник информации в регистрах ЦПЭ. Кроме того, такой режим позволяет согласовывать работу ЦПЭ с памятью и внешними устройствами, время выполнения операций в которых больше цикла ЦПЭ, путем пропуска такого количества тактов, которое необходимо для завершения операций в указанных устройствах. Прн программной реализации микропрограммы изменяются путем перемещения МК таким образом, чтобы условие перехода готовилось заранее до МК условного перехода. Алгоритм деления, преобразованный таким образом, показан на рис. 1.31; в. В этом алгоритме два условия формируются и запоминаются иа триггерах Z и С за несколько тактов до их использования. При этом число МК по сравнению с алгоритмом, показанном иа рис. 1.31, а, увеличивалось на одну, однако длина как линейной, так и циклической части алгоритма не изменилась. Если это по каким-либо причинам осуществить ие удается, то вводят две МК. первая из которых формирует н запоминает условие перехода, а вторая осуществляет по нему переход. При этом производительность процессора падает в 2 раза. При расчете длительности Го цикла процессора с КР необходимо анализировать как время Гц выполнения операции и фиксации ее результата в ЦПЭ, так и время Г формирования адреса МК в БМУ. Время Гц состоит из времени задержки в КР (30 ис для К155ТМ8), времени выполнения операции в ЦПЭ (74 ис при использовании СУП) и времени записи результата в РОН (33 ис), следовательно, Гц = 137 ис. Время Г состоит из времени задержки tsA (30 ис), времени f выборки информации из ПЗУ (70 ис), времени предустановки сигналов на входах УА (10 ис) и времени действия сигнала 5 = О (30 не), следовательно, Г = 140 не. Время Гд должно быть больше, чем max (Гц, Г ) = 140, т. е. Гд > 140 -f 3 = 143 не (длительность сигнала S == О в ЦПЭ больше на 3 не, чем в БМУ, а она должна быть одинаковой для всех ИМС ЭВМ данной конфигурации). Длина команды рассматриваемой ЭВМ (рис. 1.30, д) определяется разрядностью центрального процессора н числом обращений к ОЗУ, необходимым для выборки команды. Если потребовать, чтобы команда выбиралась за одно обращение к ОЗУ, то при принятых ранее предположениях наиболее целесообразная длина команды равна 16 разрядам. При такой длине команды более одного адреса операнда разместить в пола команды трудно, что влечет за собой применение одноадресной структуры команд, например, с 8-разрядными кодами операций и адресов. Это позволяет использовать 256 различных кодов операций и обеспечивает прямую адресацию ОЗУ емкостью 256 слов. Увеличить количество команд можно за счет более длинного кода операции, однако это требует применения двухтактной системы обращения к соответствующей микропрограмме, так как за один такт в БМУ можно ввести по шине К только 8 бит. Увеличить количество генерируемых адресов ОЗУ можно за счет применения непрямой адресации (присоединенной или относительной), а в качестве регистра базового адреса использовать одни нз РОН. При этом в системе команд должна быть команда, обеспечивающая замену со- держимого указанного регистра. Микропрограмма выполнения одноадресной команды должна обеспечивать выборку из ОЗУ очередной команды по адресу, указанному в счетчике команд,- чтение (иногда запись) операнда по адресу, указанному в команде; по коду операции - выполнение заданного алгоритма н переход к следующей команде. Для этого в РА из РОН, который выполняет функции счетчика команд, необходимо записать адрес и выдать его на ША, а содержимое счетчика команд увеличить на 1. Это можно сделать МК LMI, используя, например, регистр R0. Выбранная из ОЗУ команда фиксируется в одном из РОН ЦПЭ для дальнейшего анализа. Одновременно с фиксацией команды в ЦПЭ код операции по сигналу AM записывается в РАМК БМУ, обеспечивая тем самым обращение к первой МК микропрограммы выполнения данной команды. Так как в команде указан адрес только одного операнда, то будем считать, что второй операнд находится в АС. В этом случае целесообразно результат операции фиксировать также в АС, что облегчает его использование в качестве операнда следующей команды. После размещения операндов в соответствующих РОН микропрограмма осуществляет выполнение операции, указанной в выбранной команде. При проектировании ЭВМ важное значение имеет аппаратура обмена информацией между процессором и внешними устройствами (пульт управления, дисплей, алфавитно-цифровое печатающее устройство, ЗУ на лентах и дисках, ленточный перфоратор, программатор ПЗУ)- В рассматриваемой ЭВМ такой обмен осуществляется на основе БПП (рис. 1.30, д), который фиксирует в виде запросов сигналы готовности (Г,-, i = Tj) внешнего устройства к обмену информацией с процессором и осуществляет переход к микропрограммам обслуживания внешних устройств, состоящего, как правило, во вводе или выводе заданного массива слов в заданную область памяти и передаче управления либо прерванной программе, либо вновь введенной. Проверку наличия запросов на прерывания удобно осуществлять в конце цикла выполнения команды, так как в этом случае при прерываниях необходимо запоминать минимальный объем информации (содержимое счетчика команд и аккумулятора). Осуществляется это при переходах по МК IZR в 15-ю колонку нулевой строки {УА = 01011111) путем подачи иа вход РП БПП с выхода СРП БМУ сигнала 1. При наличии запросов на прерывание и отсутствии запрета на них как по ТЗ, так и по РТП блок приоритетного прерывания по нарастанию очередного сигнала S подтверждает прерывание {ПП = = 0). По сигналу ПП = О и коду прерывания (выходы КПО - КП2) необходимо перейти иа микроподпрограмму обслуживания внешнего устройства, вызвавшего прерывание. Это можно осуществить несколькими способами. На рис. 1.30, д сигнал ПП поступает иа вход СС БМУ, переводя выходы адреса строки в высокоомное состояние. Этот же сигнал поступает иа вход СК БПП и разрешает выдачу кода прерывания КП. Так как выходы КП (открытый коллектор) и АС (три состояния) объединены монтажным ИЛИ (гальванически связаны в одну точку и через нагрузочный резистор подключены к источнику --5 В), то на адресный вход ПЗУ поступит код, старшие три разряда которого задают КП БПП, а остальные равны 1 (высокоомное состояние выходов А5 и А4 воспринимается ТТЛ-входом ПЗУ как 1). Сформированный указанным образом код (КП2, КП1, КПО, 1, 1, 1, 1, 1,Д) будет адресом первой МК микропрограммы обслуживания, внешнего устройства, ломер которого задай на выходах КП БПП. Обращение БМУ к БПП увеличивает цикл выполнения МК, что необходимо учитывать при проектировании процессора. Предшествующий переходу иа микроподпрограмму прерывания цикл Г , должет состоять (рис. 1.32, а) из времени: задержки (30 не), цикла i ПЗУ (70 НС), задержки ty (24 не) сигнала от входов УА до выхода СРП и предустановки сигнала ip (16 ис) на входе РП БПП. Следовательно, 7 1> 30-f 70-f. 24-f 16 = 140 ис. Цикл Т перехода на микроподпрограмму (рис. 1.32, а) состоит из задержек tgn (15 не) от входа 5   до ПП БПП и (30 не), от входа СС до выхода АС БМУ, цикла ПЗУ, времени tg (10 не) предустановки сигналов УА относительно спада S II времени действия сигнала 5=0 (33 не). Кроме того, при объединении в монтажное ИЛИ выходов АС БПП (три состояния) с выходами КП БПП (открытый коллектор) вносится дополнительная задержка tk, обусловленная зарядом монтажных конденсаторов адресной шины МК при переходе выходов АС в высокоомиое состояние и зависящая от сопротивления резистора R, подключаемого между открытым коллектором выходов КП БПП и источником питания В. Величина ti уменьшается при уменьшении R (нижняя граница R определяется нагрузочной способностью выходов АС БМУ) и при R = 1 кОм 1рс= 84 НС. Следовательно, Т 2> 15 -f 30 -f 70 -f 10 + 33 -f 84 = 242 НС, что значительно больше цикла процессора (143 не), работающего без прерываний. Если цикл Т процессора принять равным Г 2, то его производительность снижается. Устранить этот недостаток можно несколькими методами. Одним из таких методов является применение генератора с переменной длительностью периода сигнала 5. В этом случае сигнал подтверждении прерывания должен переключать генератор синхросигналов на более длительный цикл, например, путем запрета одного ближайшего к спаду ПП импульса 5. Использование вместо монтажного ИЛИ коммутатора, управляемого сигналом ПП, также уменьшает Т2 величину tcA + Ir - 1к= 114 - 4, где - задержка сигнала на коммутаторе, так как переключать шину АС в высокоомиое состояние не надо. Уменьшение цикла Г 2 в этом случае может составить 100 не, однако Т возрастает на время 4, так как независимо от наличия прерывания адрес МК проходит через коммутатор. Еще более высокого быстродействия позволяет добиться схема на рис. 1.31, г, в которой БПП управляется по входу Р/7 от специально введенного в МК бита проверки наличия прерывания. В предшествующем прерыванию цикле единица в указанном бите проверяет наличие запросов иа прерывание. Если запросы есть, то по очередному нарастанию 5 БПП генерирует сигнал ПП, который через повторитель (например, К155ЛН4) устанавливает О на входе УАО. Вследствие этого, действующая в данном цикле МК IZR переводит РАМК БМУ в состояние (0,14), которое является адресом первой МК анализа вапросов на прерывания. Если запросов нет, то БМУ выдает адрес (0,15), по которому выбирается первая МК микропрограммы выполнения следующей команды. Задержки, вносимые БПП, меньше задержек, имеющихся в системе БМУ - ПЗУ. Вследствие этого цикл Тд процессора не изменяется. Недостатком данной схемы является то, что для анализа кода прерывания надо вводить дополнительные МК и связи в схеме (например, выходы КП БПП подключать к входам К БМУ). Рассмотренные этапы выполнения команды можно представить в виде графа микроалгоритма (МА) работы ЭВМ (рис. 1.32, б), вершины которого соответствуют МК ЦПЭ, БМУ и БПП. Цикл выполнения команды начинается с МКО, которая выдает на ША со счетчика команд (регистр Rg) адрес очередной команды и-начинает о(5ращение к ОЗУ путем выдачи сигналов разрешения обращения Е, считывания RD и выдачи адреса ВА. Для генерации указанных сигналов должны быть предусмотрены биты в МК. Следующая MKI завершает обращение к ОЗУ и осуществляет прием считанной с ОЗУ команды в регистр Т, а также по сигналам AM = 1 и ЗК/ = ! (IPX) осуществляет прием кода операции комаид1>1 (восемь старших разрядов) в регистр РАМК и РК. Если цикл ОЗУ больше цикла процессора, то необходимо синхронизировать их работу. Это Можно сделать многократным повторением МК1 или запретом синхросигнала 5 до завершения операции в ОЗУ (по сигналу готовности ОЗУ), или путем анализа сигнала готовности ОЗУ, который по входу Ф должен быть введен в БМУ для осуществления перехода по нему. Следующие две МК2 и МКЗ осуществляют выборку операнда из ОЗУ. При этом предполагается, что принятая в Г по МК1 команда в дальнейшем не понадобится, так как ее операционная и адресная части уже были использованы для перехода на микропрограмму выполнения команды (МПВК). Если это не так, то перед МК2 должны быть МК пересылки Т -> R . После выборки команды и операнда необходимо распределить данные в соответствии с требованиями выполняемой команды. Предположим, что выбранная из ОЗУ команда является делением чисел X и Y в соответствии с алгоритмом, показанным на рис. 1.31, в. Тогда перед началом деления X и Y необходимо разместить в R5 и R4 (МК4 - МК6), после чего осуществляется деление (МК7 - МК17). .МК18 пересылает результат в АС и сбрасывает в О триггер С, что в дальнейшем используетря как признак отсутствия останова. Если вместо деления выполняется команда останова, то последняя МК МПВК устанавливает триггер С в !. Далее по сигналу подтверждения прерывания ПП осуществляется перрод на микропрограмму прерывания МПП, которая осуществляет обмен информацией с готовым к работе ВУ. Завершается МПП анализом текущего состояния прерванной программы и вновь введенной информации, в результата которого МПП передает управление прерванной либо вновь введенной программе или осуществляет переход в состояние останова ОС. В состояние ОС процессор переходит также по сигналу Сброс , который предварительно устанавливает триггер С в 1. Так как переход в состояние останова осуществляется по сигналу сброса или после завершения ранее введенной программы, то он характеризуется отсутствием готовых к выполнению программ. Следовательно, вывод ЭВМ из состояние останова возможен после ввода готовой к работе программы, т. е. по прерыванию от внешних устройств. С этой целью осуществляется постоянный опрос сигнала ПП и при его появлении - переход на МПП. Микропрограмма работы ЭВМ при выполнении команды деления, представленная в символической форме, приведена в табл. 1.И8, а расположение МК в ячейках ПЗУ показано на рис. 1.32, в. Выборку коман-ды нз ОЗУ осуществляют МКО и МК1- Так как МК1 выполняется в том же такте, в котором выбирается МК2 из ПЗУ, то адресная часть МК2 содержит микрооперации JPX и АМ. По первой из них осуществляется запись части команды в РК, а по второй - в РАМК. При этом предполагается, что код операции деления равен 4,0 (00100,0000) и в этой ячейке следовало бы разместить первую МК микропрограммы деления. Однако для совмещения операций первая МК МПВК (общая для многих команд) помещена в ячейку 4,1 и адресация по коду операции происходит ко второй МК МПВК- Если же при выполнении команды обращения к ОЗУ за операндом не требуется (например, при командах останов и запись в ОЗУ), то считанное с ОЗУ слово в РОН не записывается. Следующей особенностью микропрограммы является анализ условия 1! при выполнении МК17, которое состоит в том, что при выборке МК17 из 62-й ячейки ПЗУ формируется адрес следующей МК в зависимости от условия, формируемого в это же время в ЦПЭ МК15. Вследствие этого указанное условие не зафиксируется в триггере С к моменту, необходимому для его использования. Однако указанное условие можно считать с триггера, что и использовано в МК17, Bvaдpecнoй части которой указан условный переход по F (JFL). МК18 осуществляет установку в О триггера С и опрос БПП путем генерации сигнала РП по JZRF, вследствие чего дальнейшие переходы определяются состоянием БПП, однако независимо от его состояния в РЛМАГ записывается код OF (000001111). Если в БПП есть запросы, то сигнал ПП = О отключает адрес строки и подает на входы ПЗУ код прерывания {КП2, КШ, КПО, 1 1, 1, 1, !, !), обеспечивая тем самым переход на подпрограмму прерывания МПП. Если запросов нет, то по ад- ресу OF выбирается МК19, в адресной части которой указан переход по JFL (триггер С по МК18 еще не успел установиться в 0). Нулевое состояние триггера F обеспечивает переход к МКО на начало выборки следующей команды. По 1 в триггере осуществляется переход к МК21 (останов), в адресной части которой код JZRF обеспечивает переход Таблица 1.1 IS

к ячейке ПЗУ OF и опрос БПП. При этом в триггер F поступает по цепи ФВ, ЦПЭ, Ф содержимое триггера С (FFC). Таким образом, БМУ попеременно генерирует адреса 5 В, Of и опрашивает 5ЯЯ до тех пор, пока на него не поступят запросы на прерывание. Переход в ОС возможен также по сигналу сброса, поступающему, например, после включения питания. Указанный сигнал поступает на вход ОС и переводит выход адреса JV1K в высокоомное состояние. Вследствие этого из ПЗУ по адресу FF (11, ..11) выбирается МК22, которая записывает 1 в триггер С н опрашивает БПП. После окончания действия сигнала сброса процессор переходит в состояние ОС нли на МПП. Рассмотренные особенности ИМС не исчерпывают всех схемных и программных возможностей 589 серии. Например, объединение в одну шину выходов внешних устройств и ОЗУ позволяет освободить шину В, к которой можно подключить сверхоперативное* ЗУ или сдвигатгль, обеспечивающий однотактный сдвиг на любое число разрядов. Подключение мультиплексора ко входу Ф позволяет расширить количество анализируемых за один такт условий. Подключение через схему ИЛИ выходов ВРК БМУ ко входам F ЦПЭ позволяет в командах адресовать РОН. Все это свидетельствует о широких функциональных возможностях и гибкости рассмотренной серии ИМС. Серия 596 [14] состоит из одной ИМС РЕ! масочного ПЗУ емкостью 8К 8-разрядных слов, основные параметры которой приведены в табл. 1.4. Отличается ИМС наличием схемотехнических средств, облегчающих ор-

ООО «Мягкий Дом» - это Отечественный производитель мебели. Наша профильная продукция - это диваны еврокнижка. Каждый диван можем изготовить в соответствии с Вашими пожеланияи (размер, ткань и материал). Осуществляем бесплатную доставку и сборку. Звоните! Ежедневно! (926)274-88-54 Продажа и изготовление мебели. Копирование контента сайта запрещено. Авторские права защищаются адвокатской коллегией г. Москвы. |