(926)274-88-54

Бесплатная доставка.

Бесплатная сборка.

График работы:

Ежедневно. С 8-00 до 20-00.

Почта: soft_hous@mail.ru

|

Звоните! (926)274-88-54 Бесплатная доставка. Бесплатная сборка. |

Ассортимент тканей График работы: Ежедневно. С 8-00 до 20-00. Почта: soft_hous@mail.ru |

|

Читальный зал --> Особенности интегральных микросхем

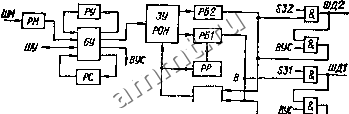

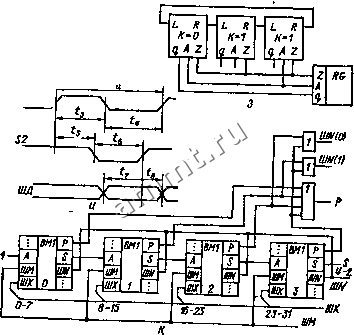

W + 30 W 4- 33 JMP Безусловный переход. Эта команда выполня- ется после команды JNC, если Q = 1 и, следс- W -L 4 вательно, очередной остаток отрицательный и его надо восстановить HLT Останов. Конец деления Таблица 1.36 Номер вывода Наименование и назначение выводов ИМС 581 ИК1 4-17, 22-23 - вход - выход 25, 26, 46 и 47-входы 27 - вход 28-34 и 36-44 вход - выход Системная шина СШ. В режиме приема информации по СШ поступают команды и данные, а в режиме выдачи - содержимое РОН Общий вывод. Шииа нулевого потенциала Ф1, Ф2, ФЗ и Ф4. Синхронизирующие сигналы, состоящие из четырех неперекрывающихся, сдвинутых по времени серий импульсов. Управление У. Единичное значение сигнала У переводит МП в режим ожидания, который используется, например, в случае ожидания поступления информации в СШ Шина микрокоманд ШМ. Шина ШМ служит для связи между ИМС комплекта и в режиме приема по ней поступают микрокоманды, а в режиме выдачи по ней выводится информация, поданная в СШ, содержимое РОНои или результаты проверки условий Питание --12 В Питание --5 В Микросхемы ВА86 н ВА87 имеют трехстабильные выходы и состоят из 16 спаренных усилителей, обеспечивающих передачу 8-разрядиого кода в прямом или обратном направлении. Управляются ИМС сигналами выбора кристалла и кода операции, задающего направления передачи информации. Отличается ВА87 от ВА86 тем, что осуществляет инверсию передаваемой информации. Серия 581 (5, 17, 19, 21, 30] состоит из ИМС ИК1 и ИК2; РУ1 - РУ4; ВА1 и ВЕ1, параметры которых приведены в табл. 1.4. Серия предназиачеиа для построения специализированных вычислительных устройств и широко применяется в микро-ЭВМ Электроника-60 . Процессорный элемент ИК1 представляет собой 8-разрядное АЛУ, в котором на микропрограммном уровне реализована обработка 16-раз-рядиых слов. Назначение выводов ИК1 приведено в табл. 1.36. Восьмиразрядный арифметический блок АБ выполняет 84 операции (сложение, вычитание, ±1, +2, сдвиги, поразрядные конъюнкции и дизъюнкции). Двадцать шесть 8-разрядиых регистров общего назначения РОН объединены 45 - вход 48 - вход дешифратором Д в ЗУ РОН, схемная реализация которого обеспечивает П1раллельнуювыдачу в Л£ или в системную СШ или микропрограммную ШМ шииу содержимого двух РОН (рис. 1.17, б). Режим работы ИМС определяется микрокомандой, записанной в регистр РМ и состоящей из кода регистровой операции и адресов РОН, участвующих в операциях. В микрокомандах условных переходов или с непосредственной адресацией разряды ш адресов используются либо для указания номера проверяемого условия, либо для записи одного из операндов. При этом 10 РОН адресуются прямо путем задания их номеров в соответствующих полях микрокоманды, 4 РОЯ адресуются либо прямо, либо косвенно, а остальные 12 РОН адресуются только косвенно с помощью 3-разрядиого регистра указателя адреса РУА. Из 10 регистров первого типа образуют пять 16-разрядных регистров, которые используют как рабочие регистры микропрограмм для хранения команды, исполнительного адреса, двух опейидов и слова состояния микропрограммы. Четыре регистра второго типа используют как указатель стека и счетчик адреса команд. Остальные 12 регистров используют как шесть 16-разрядиых регистров общего назначения. Системная информация, состоящая из команд и данных, поступает в ИМС ИК1 по 16-разрядной СШ, состоящей из двух 8-разрядиых шии, и с помощью мультиплексоров МА, MB и Л1С может заноситься в РОН или передаваться в ШМ. Микрокоманды, подлежащие исполнению, поступают в МС по ШМ и по сигналу Ф1 фиксируются на РМ. Код операции микрокоманды с РМ поступает в блок местного управления БМУ, который по Ф2 и ФЗ вырабатывает управляющие сигналы УС, обеспечивающие выполнение заданной микрооперации. Обработка 16-разрядиых слов одной микрокомандой осуществляется за два цикла за счет того, что во втором цикле младшие разряды номеров регистров, указанных в микрокоманде, инвертируются и над содержимым регистров, номера которых полу>1еиы указанным образом, выполняется та же микрооперация. За время действия тактовых сигналов ФЗ и Ф4 происходит подготовка к приему следующей микрокоманды или к выдаче информации в ШМ или СШ. В последнем случае информационные сигналы усиливаются выходными усилителями ВУ1 и ВУ2. При выполнении операций в АБ вырабатываются признаки отрицательного и нулевого результата, 4- и 8-разрядиого переносов и переполиеиня, которые в регистрах признаков РП и с помощью схемы анализа САП проверяются микрокомандами условного перехода. Микросхема ИК2 (рис. .17, в) представляет собой блок микропрогра.м-много управления н предназиачеиа для управления работой процессора микро-ЭВМ Электройика-60 , построенного иа основе ИК1. Назначение выводов ИК2 приведено в табл. 1.37. Основными функциями ИК2 является формирование адресов микрокоманд и управление системной шииой СШ. Основным узлом МС является счетчик микрокоманд СМ, содержимое которого увеличивается иа единицу при каждом обращении к ПЗУ микропрограмм. Формирование и последующая запись в СМ адресов начала микропрограмм и адресов условных и безусловных переходов осуществляются комбинационной схемой КС, которая, в свою очередь, управляется содержимым регистров системной команды РК, микрокоманды РМ, прерываний РП и состояний PC, а также внешними управляющими сигналами ВУС. Для запоминания адреса возврата из подпрограммы служит регистр РВ. Внутренние управляющие сигналы УС и сигналы управления системной шиной вырабатывают соответственно БМУ и БУСШ, которые управляются содержимым РМ через дешифратор операции ДО. Микропрограммы обработки информации записаны в ПЗУ РУ1, РУ2 и РУЗ, где хранятся соответствеиио первая, вторая и третья страницы управляющей информации. Обращение к страницам осуществляется путем задания 2-разрядиого кода выбора ИМС, который дешифрируется схемой, встроенной в ПЗУ иа стадии изготовления БИС. Вследствие этого отпадает необходимость применять внешние селектирующие схемы. Четвертая комбинация кода выбора ИМС зарезервирована для ПЗУ, содержащих микропрограммы пользователя, что повышает эффективность применения МП и позволяет приспосабливать программное обеспечение к классу решаемых задач. Для построения оперативной памяти можно использовать ИМС РУ4, динамического типа емкостью I6K одноразрядных слов. ИМС потребляет 420 мВт от двух источников -5и 12В. Время выборки 135 нс. В описанный Таблица 1.37 Номер вывода Наименование и назначение выводов ИМС 581 ИК2 4-7 Входы для подачи сигналов прерывания от внеш- него устройства, по таймеру, питанию и регенерации ОЗУ 8 и 12 Входы для 17-го и 16-го разрядов микрокоманды 9-11, 13 и 14 Входы для управляющих сигналов: занято, до- полнение, сброс, готово и ожидать 15-17, 22 и 23 Выходы сигналов управления системным каналом: вывод данных, запись байта, подтверждение пра-рывания, синхронизация и ввод данных 24 Шина нулевого потенциала 25, 26, 46 и 47 Входы для подачи тактового питания Ф1-Ф4 27, 45 и 48 Входы для подключения питающего напряжения -5, -12 и -5 В 28-34, 36-44 Шина микрокоманд ШМ, работающая в режиме двусторонней передачи информации набор входит также универсальный асинхронный приемопередатчик ВА1 rt однокристальная микро-ЭВМ BEI. , Серия 582 [8, 19, 28] состоит из пяти ИМС, которые выпускаются в корпусах 244.48-8, 413.48-3 (см. табл. 1.4). Основными ИМС являются процессоры ИК1 и ИК2, которые имеют выводы, обеспечивающие увеличение разрядности с дискретностью в 4 бит. Кроме МП серия содержит ИМС запуска (ИКЗ), ПЛМ (ИК41.....ИК47) и прерываний (ИК5). Микропроцессорный набор данной серии по архитектуре во многом подобен серии 584. Показатели ИМС этой серии уступают рекордным показателям серий ТТЛШ и ЭСЛ по быстродействию, серий яМДП по степени интеграции, серий КМОП по энергопотреблению и серий рМОП по стоимости. Вместе с тем ИМС И*Л серий лишены и многих недостаков, которые имеются в указанных сериях (например, большое энергопотребление у серий ЭСЛ и ТТЛШ), поэтому их эффективно применяют в областях, где ие требуется экстремальных значений отдельных показателей. Серия 583 (11, 18, 19]. Основньке параметры серии приведены в табл. 1.4 и 1.38. Центральный процессорный элемент ВС1 состоит (рис. 1.18, а) из арифметического устройства Л У, запоминающего устройства ЗУ в виде 16 регистров общего назначения РОН, блока управления БУ, вырабатывающего внутренние управляющие сигналы ВУС, и вспомогательных регистров результата РР, управления РУ, состояния PC, микрокоманды РМ и двух буферных регистров РБ1 и РБ2. Регистры РМ и PC состоят соответственно из 16 н 2 разрядов, а остальные - нз восьми. Следует отметить, что кроме описанных регистров других запоминающих элементов ни в БУ, ни в ЛУ  f к-о Л-; I-, о -г- t t  Рис. 1.18 4 5-2143 ИМС 583 серии Функциональное назначение Разрядность, бит Р, мВт

ВА1 Приемопередатчик магистральный с памятью ВА2 без памяти ВАЗ Универсальный коммутатор ВА4 Коммутатор магистралей ВГ1 Контроллер - синхронизатор ВГ2 Контроллер предварительной обработки информации ВМ1 Микропроцессор логический ВС1 Центральный процессорный элемент ВС2 Умножитель вез Арифметический микропроцессор ВС4 Универсальный микропроцессор ВУ1 Масочная программируемая логическая матрица ИК1 Генератор адресов микрокоманд КП1 Коммутационный микропроцессор РА1 Ассоциативное запоминающее устройство ХЛ1 Коммутатор магистральный ИМС не имеет и построена исключительно на КС Обмен информацией осуществляется по двум двунаправленным шинам данных ШД и ШД2, шине микрокоманд ШМ и неоднородной шине управления ШУ, включающей в себя одно- и двунаправленные выводы и служащей для ввода или вывода управляющих сигналов, а также для каскадирования ИМС при увеличении разрядности, кратной 8 (табл. 1.39). Микросхема работает с числами, представленными в дополнительном коде. Для указания знака отводится один (старший) разряд, который отделяется от мантиссы числа фиксированной запятой. Выделяется знаковый разряд сигналом К на входе ЗУ. При К = 1 все разряды чисел в даииой ИМС обрабатываются как разряды мантиссы. При/С = О старший разряд обрабатывается как знаковый, а все остальные- как разряды мантисс. Отличия в обработке знакового разряда и разрядов мантисс проявляются при переполнении разрядной сеткн и прн сдвигах. Под переполнением понимается выход результата за пределы диапазона (-1, 1). Это возможно при сложении на сумматоре чисел одного знака, сумма которых по модулю больше 1. Переполнение разрядной сетки сопровождается появлением сигнала q - 1 (выход 29), который формируется по правилу Я=К (Ml V Ш) V Kq , где - перенос из знакового разряда; qi - перенос из старшего разряда мантиссы в знаковый разряд. Такое правило формирования сигнала q объясняется тем, что прн переполнении разрядной сетки перенос в знаковый разряд сопровождается отсутствием переноса из знакового разряда или отсутствие переноса в знаковый разряд сопровождается переносом из знакового разряда. Так как переполнение связано с ошибочным изменением знака, то ИМС восстанавливает его. Если же переполнения разрядной сетки нет, то ?о = Qi-При К - 1 переносы q = q не анализируются, так как на месте знакового разряда находится старший разряд нз данной группы разрядов мантиссы н его обработка осуществляется так же, как и остальных разрядов мантиссы. Номер вывода Назначение выводов ИМС Б83ВС1 в корпусе 244.48-8 / i Входы синхросигналов приема S1 и выполнения S2 МК н выдачи результата на ШД1 (S31) и Д/Д2 (S32) 5 7 Шина микрокоманд, номера разрядов которой образуют 35-47 ряд 5-7, 4-0, 8, 12, 13, 9, 14, 10, 15 н 11 8-23 Шнны данных ШД1 и ШД2. Четные номера выводов соответ- ствуют ШД/, а нечетные - ШД2 24 Шина нулевого потенциала 25 , 48 Гальванически связанные в одну точку иыводы, слуящив для подключения ИМС к источнику пнтання через токозадаю-щий резистор. Величина питающего напряжения Е должна быть не меньше 1,2 В, а сопротивление R резистора определяется по формуле /?=(£- 1,2)11, где / - питающий ток (225 < / < 345) мА 26 и 33 Правый R и левый L двунаправленные выводы сдвигателя АУ 27 Вход С сигнала переноса сумматора АУ 28 Выход признака нуля результата (признак Z) 29 Многофункциональный выход q, служащий при /С О для индикации переполнения разрядной сетки, а прн /С я 1 - для вывода сигнала переноса из старшего разряда сумматора у4У 30, 31 Выходы сигналов распространения Р и образования <? груп- пового переноса 32 Многофункциональный выход А, индицирующий при выпол- нении арифметических операций (пц= щ = G) состояние знакового разряда, а прн сдвигах {щ=*т1= 1) - разряд, выходящий в результате сдвига за пределы разрядной ветки (выдвигаемый разряд). При левых сдвигах - это нулевое или первый разряд старшей ИМС (К = 0), а при правых сдвигах - седьмой разряд самой младшей ИМС 34 Вход К, задающий позицию ИМС (старшая прн К *= О, млад- шая при /С = 1), а следовательно, и способ обработки чисел в ИМС Примеры действий с числами в старших (К = 0) н младших (/С = 1) ИМС приведены в табл. 1.40. Другое огличне в обработке знакового разряда и разрядов мвнтнссы проявляется при сдвигах, особенности реализации которых поясняют m левом арифметическом сдвиге ЛАС в старшей ИМС (Л - 0) знаковый разряд (отмечен цифрой 0) отключается от остальных разрядов н в сдвиге не участвует (рнс. 1.18,6). Все разряды мантиссы перемещаются на одну позицию влево, в младший разряД младшей ИМС (АГ - 1) записывается О, а старший разряд мантиссы (отмечен цифрой 1) старшей ИМС tnul ° °ДЯ1Цнй за пределы разрядной сетки после завершения сдвига пд! пА*!/ разряд), выдается на выход А. Прн правом арифметичком пяпа знаковом разряде не изменяется) (рис. 1.1$, д) все рчлряды мантиссы перемещаются на одну позицию вправо, в старший разр яд

ООО «Мягкий Дом» - это Отечественный производитель мебели. Наша профильная продукция - это диваны еврокнижка. Каждый диван можем изготовить в соответствии с Вашими пожеланияи (размер, ткань и материал). Осуществляем бесплатную доставку и сборку. Звоните! Ежедневно! (926)274-88-54 Продажа и изготовление мебели. Копирование контента сайта запрещено. Авторские права защищаются адвокатской коллегией г. Москвы. |