(926)274-88-54

Бесплатная доставка.

Бесплатная сборка.

График работы:

Ежедневно. С 8-00 до 20-00.

Почта: soft_hous@mail.ru

|

Звоните! (926)274-88-54 Бесплатная доставка. Бесплатная сборка. |

Ассортимент тканей График работы: Ежедневно. С 8-00 до 20-00. Почта: soft_hous@mail.ru |

|

Читальный зал --> Особенности интегральных микросхем -\A1 \ SM 52 pit

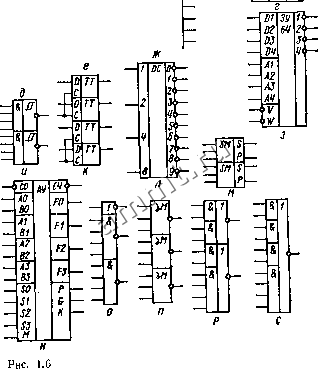

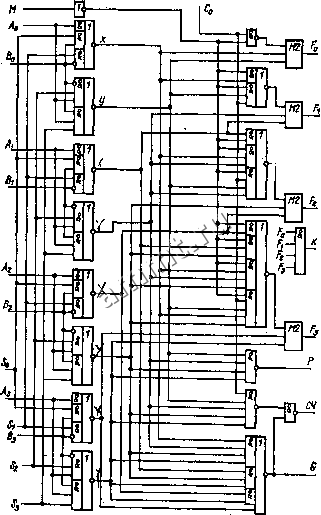

сывается цифра со входа DO. При остальных состояниях входов V, С1 и С2 осуществляется хранение заиесеииой в ИР 1 информации. г, п Регистр ИВЙ* (рис. 1.6, J) реализует МО установки О при = О, левого сдвига при J? = So = Si = 1, правого сдвига при R = So = Si = 1 и приема кодов с входов DO = D7 при /?= Se= Si= 1. Указанные МО выполняются по нарастанию сигналу С. При левом (правом) сдвиге в 7 (0)-й разряд заносится цифра с входа DL(DK). При других комбинациях сигналов на входах R, SO, St и С реализуется режим хранения. Регистр ИР17 (рис. 1.9, а) имеет установочный вход S, сигнал О иа ко- тором устанавливает триггеры 0-10 в состояние 1 (Qc= 1), а разряд 11- в 0. Поступающая иа вход D информация по нарастающему перепаду сигнала С записывается в старший свободный разряд (в такте 1 - в разряд 11, в такте 2- в разряд 10, в такте 3- в разряд 9 и т. д.), а следующий младший устанавливается в О, что является признаком его готовности принять информацию в следующем такте. Поступившая в данном такте информация для контроля фиксируется также иа специальном триггере с выходом DO. Признаком заполнения регистра является появление сигнала О иа выходе СС, по которому триггеры ИР 17 блокируются от входов D и С, и записанная инфмация хранится до поступления очередного сигнала 5=0. Для каскадирования в ИМС предусмотрен вход разрешения Е, единица иа котором блокирует изменение состояний регистра. Основное иазначеиие ИР17- работа в АЦП поразрядного взвешивания, в преобразователях последовательного кода в параллельный, кольцевых счетчиках с бегущим нулем и схемах управления. Коммутатор КП2 реализует две функции 1/1 = (ABDi У ABD У ABDa у ABD \; 1/2 = (ABD У ABD у ABD, у ABD) \. Коммутатор КП5 реализует функцию А при а = 1; Л при а=0. а, р, Y - разряды двоичной записи числа (, представленной в виде аРу. Коммутатор КП7 реализует функции 2 = yR и ?2 = yk, где у определяется выражением (1). Микросхему ЛА1 (рис. 1.6, д) можно использовать как два элемента И - НЕ иа четыре входа или как элемент И - НЕ и И - ИЛИ - НЕ при подключении ко входам АВ расширителя И - ИЛИ. Логические элементы ЛА7 и ЛА8 предназначены для работы на ие-стаидартиую нагрузку (реле, светодиоды) и позволяют коммутировать ток до 40 мА. Наличие открытого коллектора позволяет реализовать монтажное ИЛИ с большим коэффициентом объединения. Все элементы ИЛИ - НЕ, И и ИЛИ ИМС ЛЕ1, ЛИ1 и ЛЛ1 имеют по два независимых входа. Микросхема ПП4 (рис. 1.6, ж) служит для преобразования двоично-десятичного кода 8D -f- 4С-f- 2S -f- Л в код возбуждения семисегментно. го цифрового индикатора и реализует следующие функции: Qi = ЛС V V ABCD У V; = BD V ABC у ABC у V; С?з = CD V ЛВС yV; = ЛВС V ЛВС V ЛВС V V; Q = AyBCyV; Q, = AByBCyACDyV; Q, = ЛВС V BCD У V. Микросхема РУ1 является функциональным аналогом ИМС 100РУ401 (см. рис. 1.2, л). Информация с входов РУ2 (рис. 1.6, з) записывается при V = IF = О в ячейку, адрес которой задан иа входах Л,-, при этом осуществляется считывание без разрушения информации по адресу Л1Л2Л3Л4. При остальных значениях сигналов V и W осуществляется режим хранения, при котором выходы ИМС находятся в состоянии 1 (В/ = У = 1) или повторяют состояния входов {W = V = I). При использовании нескольких ИМС РУ2 нли РУ1 выходы их можно объединять в монтажное ИЛИ. На основе триггера Шмитта в ИМС ТЛ1 (рис. 1.6, и) реализован ло-. гическнй элемент И - НЕ повышенной помехоустойчивости, который надежно работает при больших длительностях нарастания или спада сигналов. Это свойство используют для построения формирователей и генераторов сигналов. Триггеры ИМС ТМ2 (рис. 1.3, л) построены по схеме трех триггеров (рис. 1.4, б). Переключение основного триггера ТЗ, а следовательно, и изменения сигналов Q и Q происходят по нарастающему фронту сигнала на входе С (рис. 1.4, б). Если при этом D = 1/0, то на выходах схем И4 и И1 будут действовать сигналы 0/1 и 1/0 соответственно, которые через схемы И2 и ИЗ обеспечат установку ТЗ в состояние 1/0. После того как сигнал I установится на входе С и завершатся вызванные этой установкой переключения схем И2, ИЗ, И5 н И6, сигналы на выходах И2 и ИЗ, воздействуя на И1 и И4, заблокируют свои входы, вследствие чего изменение состояния входа D не будет вызывать переключений ТЗ. Соединив вход D с выходом Q, получим Т-трнггер, изменяющий свое состояние по каждому нарастающему перепаду сигнала на входе С. Триггеры ТМ5 (рис. 1.6, к) и ТМ7 переключаются по нарастанию сигнала С. ИМС ТМ7 отличается от ТМ5 наличием как прямого, так и инверсного выходов. Серия 134 1, 15, 24, 28] состоит из ИМС (табл. 1.4 и 1.6) ИДЗ и ИД6, ИЕ2 и ИЕ5, ИМ4 и ИМ5, ИП2 - ИП4, ИР1, ИР2, ИР5 и ИР8, ЛА2 и ЛД8, ЛБ1 и ЛБ2, ЛПЗ, ЛР1, ЛР2 и ЛР4, КП8, КП9 и КПЮ, РМ1, РУ6, СП1, TBI н ТВ 14, ТМ2 и ХЛ2 и ХЛЗ. Быстродействие ИМС имеет значительный разброс: 70 ис для ИМС с индексом Б (например, ЛБ2Б), 100 не для ИМС с индексом А и 200 не для ИМС без индекса. Дешифратор ИД6 преобразует двоично-десятичный код в сигнал О иа выбранной шине (рис. 1.6, л). Сумматор ИП2 реализует функции Sj = DVi V DV; =4DV V DVi, где D = D,-(mod2); D,-, Vj и Vj -вЛдные переменные ИМС. г=о Арифметическое устройство ИПЗ (рис. 1.6, я и 1.7) является КС, состоящей из трех каскадов. ПерввЛ каскад выполняет логические операции над разрядами Л,- и В, операндоРЛ и В: XI = Ai V B,Se V йлДГТХвА. дли которых справедливы тождества xtyi = xf. х,ус = Ус; Xi У У1= УГ. Xi V ~у1 = Xi. Второй каскад формирует сигналы переносов, соответствующие переносам Qi, возникающим при суммировании чисел, j-e разряды которых равны соответственно xi и ( : II Г Я* I-11- -Уз Ун ?о = С Уо F Ft Fi F,  Рис. 1.7 Следовательно, 90 = о; Ь = xi V {Х2 V У2) qi\ Qi = хУо V (Хо V У о) fi = Х3У3 V (3 V 3) Q3, 1г = хУ1 V (1 \1у%)Я1 или с учетом тождеств (2) получим = Q, (?1 = i/o V xfia. 92 = У1 V 1Уо V ЧХ,; 3 = 2 V ~х,У1 V xiio V WoCol у yj V 4-V WiJ/o V Выражение для можно преобразовать следующим образом: 9i = й V ЧСо = г/о (оо) = Уо ( V С ) = у< V УоС = 0 V !/ С . Таблица 1.8

А АуВ АуВ \ АВ S АВУАВ Ау В ~АВ АВ\1АВ fl АуВ О АВ АВ А А + (АВ) А + АВ А+А АуВ (АУВ1+АВ А+В (АУВ)+А АуВ Л + В (АУВ) + АВ {АУВ) + А ЛВ+ 1 ЛВ-f 1 Л + 1 ную {М), функции, аналогичным образом преобразовать q, ?з и 94 и ввести перемеи-блокирующую при уИ = 1 распространение переноса, то получим реализуемые вторым каскадом ИМС: = XiM У yxj V ViUiXoM У УУгУоСоМ; 94 = {УзУгУуУоо) (Ч У ух V Ух у yyix) = (У3У2У1У0С0) О, где G = х у у2 у yyXi У У3У2УЛ. При М = I эти схемы отключаются, вследствие чего ИПЗ реализует только поразрядные операции. Третий каскад состоит из сумматоров по! модулю 2 (рис. 1.7), на которых формируется окончательный результ логической (при М = I) или арифметической (при М = 0) операции Реализуемые операции приведены в табл. 1.8, где Л = Л; и В = В,-. Вй реализуемой поразрядной операции легко определить, если учесть, па входы сумматоров поступают л:,-, у,- и 1. Следовательно, f, = (ЛТУвЛЛЛёА) + 0iBiS, У AiBiSs) + 1 (mod2). Так как а = а + 1 (mod 2)иа\/ Ь- а+ Ь-\- аЬ (mod 2), то после преобразования получим f ( = Л( + ЛгВ,5 + Л,В,51 + AiBiS + Л,В,5з (mod 2), Например, при S = (1, О, I, 0) F = Л,- -f Л,В,- + Л(В,- (mod 2) = Л,- + 1 + ЛВ, + В, + Л( -f Л,В( (mod 2) = = В,- + 1 = В,. При Л1 = О схема переноса не блокируется и на сумматорах формируются сигналы с учетом поразрядных переносов: ~Х1+т+ qt (mod 2) = (Л( V B,S V + (ASa V AiBiSt +qt (mod 2). Сигнал К = f oi28 можно использовать как признак того, что для всех разрядов = у( (М - I) или -f г/; = 1. Например, при S = = (1, О, О, 1) и М = 1 или S = (О, 1, 1, 0) и М =£ = О равенство К = 1 означает, что Л = В. Перенос из ИПЗ возникает, если он образуется в 3-м разряде или если он образуется во 2-м разряде и проходит через 3-й, или если он образуется в 1-м и проходит через 2-й и 3-й, или если он обра-; зуется в нулевом и проходит через остальные разряды, т. е. если 33 V (3 V Уз)(х2Уз) У (хз У Уз) (Xi У й) (хт) У У У Уз) (X, У ~У2) {Xl У У1) (i V Уо) = 1 С учетом тождеств (2) это условие можно переписать в вида Уз V V 321 V XiXjy = I (3) Перенос из ИПЗ может также возникать, если есть перенос в данную МС и он пройдет через все разряды, т. е. {Хз У Уз) (Xi У У2) (Xl У Ух) (ха У Уо) = XtXiiXg = I. Условия (3) и (4) используют для формирования сигналов Р = У31/2У1У0 = </з V </2 V У1 V !/о G = дгз У Узх У УзУ1 у УзУУхХо =УзУ ху У хху V 3*2*1*0. предназначенных для управления схемой распространения быстрого (группового) переноса. Действительно, если условие (3) выполняется, то , = Уз V 32 V xiVi У з 2 1зд) = УзУ х2 У ХзХгУ1 У хХхУе = 1. так как ху = Если условия (4) выполняются, тоО = 1. Следовательно, PG можно рассматривать как сигнал переноса, возникший в данной МС ИПЗ, а G - как условие прохождения через ИПЗ сквозного переноса. Сигнал 0= 1 может появиться, когда .условие (4) и не выполняется, но это не вызовет ложного сквозного переноса, так как из условий 0 = = 1 и Х3Х2Х1ХВ = О следует, что Р = 1 и PG = 1. Схема ускоренного переноса ИП4 предназначена для формирования группового переноса через четыре ИМС ИПЗ и реализует следующие функции; Сз = Pfi у GPiGi у GGiPfi, У G,GiG,C,; Р=Р У Р1У Р,У Рз. G = P3G3 У G3P2G2 У GfiPyGi у GfifiG 2 5-2143 33

ООО «Мягкий Дом» - это Отечественный производитель мебели. Наша профильная продукция - это диваны еврокнижка. Каждый диван можем изготовить в соответствии с Вашими пожеланияи (размер, ткань и материал). Осуществляем бесплатную доставку и сборку. Звоните! Ежедневно! (926)274-88-54 Продажа и изготовление мебели. Копирование контента сайта запрещено. Авторские права защищаются адвокатской коллегией г. Москвы. |

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||