(926)274-88-54

Бесплатная доставка.

Бесплатная сборка.

График работы:

Ежедневно. С 8-00 до 20-00.

Почта: soft_hous@mail.ru

|

Звоните! (926)274-88-54 Бесплатная доставка. Бесплатная сборка. |

Ассортимент тканей График работы: Ежедневно. С 8-00 до 20-00. Почта: soft_hous@mail.ru |

|

Читальный зал --> Особенности интегральных микросхем в 6-вМ- разрядах ПЗУ информация кроме того позволяет использовать ПР6 в качестве преобразователя двоично-десятичной цифры в код, дополняющий эту цифру до 10 (у = 10 - л;) и до 9 (у = 9 - х). Схемы, осуществляющие эти преобразования, показаны иа рис. 1.9, д и е. Указанные преобразования выполняются при К = О, при К = 1 на всех выходах ИМС выдается сигнал 1. Таблица 1.10

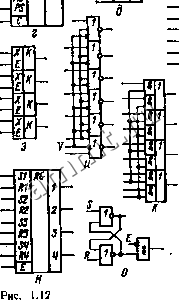

Преобразователь ПР7 (рис. 1.9, в) построен на основе ПЗУ и осуще- ствляет перевод целого двоичного числа в диапазоне от О до 63 в эквивалентный ему двоично-десятичный код с весами 8, 4, 2, 1. Так как цифры в младших разрядах двоичного и двоично-десятичного числа равны, то в ПЗУ записана таблица соответствий между 2, 3, 4, 5 и 6 разрядами двоичного числа и 2, 3, 4, 5, 6 и 7 разрядами двоично-десятичного числа (2, 3 н 4 разряды относятся к первой декаде, а 5, 6 и 7 разряды - ко второй). Младший разряд десятичного числа формируется так же, как и при обратном преобразовании (рис. 1.9, г) при К = О, а при К = 1 на выходах ИМС генерируется сигнал 1. На выходах Q7 и Q8 сигнал 1 удерживается при любых комбннацяях сигналов иа входах. Постоянное ЗУ РЕЗ (рис. 1.9, в) емкостью 32 8-разрядных слов допускает однократную электрическую запись информации на специальном устройстве, называемом программатором. Группа ИМС РЕ21-РЕ24 построена на основе ПЗУ с записанной прн изготовлении информацией н используется в качестве преобразователей двоичного кода в коды знаков русского (РЕ21) и латинского (РЕ22) алфавитов, арифметических знаков и цифр (РЕ23) и дополнительных знаков (РЕ24). Оперативное ЗУ (рис. 1.9, ж) РП1 имеет независимые каналы для записи и чтения информации, вследствие чего эти операции можно совмещать во времени. При VW - О слово со входов D записывается по адресу, указанному на входах Wi и W. При VR = Q слово считывается с ячейки, адрес которой задан на входах RI, R2. При VR = 1 на выходах ИМС устанавливается сигнал 1. Выходные каскады ИМС построены на транзисторах с открытыми коллекторами, благодаря чему можно объединять до 64 входа ИМС в монтажное ИЛИ. функциональное назначение (номер поясняющего рисунка) АП ИД1 ИД2 ИД4 ПД5 ИЕ1 ИЕ2 ИЕЗ ИЕ4 ИЕ5 ИЕ8 ИЕ9 НЕЮ ИЕ11 ИЕ12 ИЕ13 ИЕ14 ИЕ15 ИЕ16 ИЕ17 ИЕ18 ИЕ19 ИК1 ИМ1 ИП2 ИПЗ ИП4 ИП5 ИР12 ИР 13 КП1 КП2 164, 176, 564 176 564 564 164, 176 164, 176 176 176 176 176, 561 564, 561 564. 561 564, 765, 561 176 564 564 561 176 176 564 564 164, 176, 564, 561 564, 561 564, 561 164, 564 164, 176, 564 164, 176 176 564, 561 564, 765, 561 164. 176 564, 561 564, 561 564 564, 561 564 Два одновибратора Дешифратор 4Х 10 (1.4, г) для 7-сегментиых ин- дикаторов Дешифратор для 7-сегментных индикаторов Дешифратор возбуждения Стробируемый дешифратор возбуждения Двоичный счетчик (1.10, з) Двоично-десятичный счетчик (1.10. и) Счетчик по модулю 6 (1.11, и) 10 Делитель частоты 15-разрядиый (1.П, к) Десятичный счетчик (1.11, л) Счетчик двоичный (1.11, н) Два 4-разрядных счетчика (1.11, о) Реверсивный 4-разрядный счетчик (1.12, а) Счетчик по модулю 60 и 15-разрядный делитель частоты Двоичный счетчик Двоично-десятичный счетчик Программируемый счетчик 14-разрядный счетчик-делитель Двоичный счетчик-калеидарь Счетчик по модулю 60 5-разрядиый счетчик Джонсона Строенный мажоритарный мультиплексор Сумматор 4-разрядиый Компаратор 4-разрядный (1.12, б) Арифметическое устройство (1.6, н; Схема ускоренного переноса Схема умножения 2-разрядиая (1.12, в) Регистр 18-разрядиый (1.10, к) Два регистра 4-разрядиых (1.11, г) Реглстр 4-разрядный (1.11, д) Регистр 8-разрядиый 8-разрядиый (1.12, г) 4-разрядный (1.12, д) 18-разрядный (1.10, к) Многоцелевой регистр 8X4 (1.12, е) 4X4 12-разрядиый регистр последовательного приближения Два мультиплексора 4X1 (1.12, ж) Мультиплексор 8X1 (1.2, г) функциональное назначение (номер поясняющего рисунка)

Четыре двунаправленных переключателя (1.12, з) Четыре двунаправленных переключателя (1.12, з) Четыре элемента 2И-НЕ Два элемента 4И-НЕ Три элемента ЗИ-НЕ Два элемента 2И-НЕ с открытым стоковым выходом Четыре элемента 2ИЛИ-НЕ Два элемента 4ИЛИ-НЕ Три элемента ЗИЛИ-НЕ Элемент 9И и элемент НЕ Шесть стробируемых элементов ИЛИ-НЕ (1.12, и) Шесть элементов НЕ Универсальный элемент Сумматоры по модулю 2 (1.11, е) Два элемента ЗИЛИ-НЕ и элемент НЕ Два элемента 4ИЛИ-НЕ и элемент НЕ Два элемента 4И-НЕ и элемент НЕ Три мажоритарных элемента Три элемента И-ИЛИ (1.1), ж) Четыре элемента И-ИЛИ (1.12, к) Коммутатор 8Х1 аналоговых сигналов (1.2, г) Пять преобразователей уровня с инверсией Шесть преобразователей уровня с инверсией То же Преобразователь уровня Четыре преобразователя уровня Шесть преобразователей уровня с инверсией То же ОЗУ 16Х 1 ОЗУ 256X 1 (1.11, л) Сумматор по модулю 2 иа 13 входов Два JK-триггера (1.11, з) - Четыре триггера Шмитта Два D-триггера (1.11, п) Два D-триггера / Четыре D-триггера (1,12, л) Четыре RS-триггера (1.12, м, о) Усилитель индикации Электрическая схема накопителя и принцип работы МС РУЗ (рис.1,9, з) аналогичны ИМС 100РУ401 и отличаются тем, что для записи О (1) необходимо совпадение сигналов 1 на входах ХО (XI). Выходы РУЗ выполнены как транзисторы с - открытым коллектором, поэтому их можно объединять в монтажное ИЛИ, Триггеры ИМС ТМ8 (рис. 1,9, к) переключаются по нарастающему перепаду сигнала С при условии, что /? = 1. Серия 158 [28J состоит из ИМС ЛА1-ЛА4, ЛР1, ЛРЗ, ЛР4 и TBI, которые описаны в предыдущих разделах (см. табл, 1,4 и 1,6), Серия 164 [1,10], Микросхемы данной серии и аналогичных по логическим возможностям серий 176.561, 564 , 764 и 765 относятси к КМОП-типу и имеют следующие особенности: 1) работают при питающем напряжении 3-18.В; 2) верхний и нижний пределы напряжения ограничены 5 и 15 В, так ка К при меньших напряжениях теряется быстродействие и снижается помехоустойчивость, а при напряжениях, больших 15 В, увеличивается потребляемая динамическая мощность и интенсивность отказов от перегрева; 3) зависимость потребляемой мощности от частоты переключения ИМС, В статическом режиме потребляемая мощность обусловлена токами утечки и составляет 0,1 мкВт на вентиль. При переключении появляется Динамическая составляющая потребляемой мощности, обусловленная как необходимостью перезарядки монтажных конденсаторов, так и наличием в течение короткого интервала времени сквозного тока через оба транзистора и- и р-тта, составляющих вентиль КМОП-схем, При емкостное нагрузке 15 пФ и питающих напряжениях 5, 10 и 15 В динамическая рассеиваемая мощность равна соответственно 8 10 *; 3 10~j 7 10 Вт/Гц и возрастает пропорционально емкостной нагрузке. Серия состоит из ИМС ИД1, ИЕ1 и ИЕ2, ИМ1, ИР1-ИРЗ и ИРЮ. ИТ1. КТ1, ЛА7-ЛА10. ЛЕ5 и ЛЕ6, ЛИ1. ЛП1, ЛП2, ЛП4, ЛПП и ЛП12, ЛС1, ПУ1, РМ1. TBI и ТМ2. Основные характеристики и функциональное назначение серии приве* дены в табл. 1.4 и 1.11, Двоично-деситичный счетчик ИЕ2 (рис. 1.10, и) имеет четыре входа 5; предварительной установки, состояния которых при V = 1 фиксируются иа триггерах ИМС, Сигнал 1 (0) на входе 2/10 определяет режим двоичного (десятичного) счета, который происходит при V = 0. При десятичном счете сигнал переноса формируется на выходе Р. Сумматор ИМ1 имеет девять входов дли nepeH(ca и двух 4-разрядных чисел и пять выходов суммы. Микросхема ИР1 (рис. 1.10, к) содержит четыре регистра длиной соответственно в 5, 4, 5 и 4 разряда с общей синхронизацией, переключаю-щихси по спаду. Пятиразрядные регистры имеют выходы с 4-го и 5-го разрядов, благодаря чему можно формировать регистры длиной в 4, 5, 8-10, 12-14, 16-18 разрядов. Информация в регистрах ИР2 (рис. 1.11, г) при R = О сдвигается по нарастанию сигнала С, а по сигналу R = i триггеры регистра устанавливаются в О, Регистр ИРЮ (рис. 1.10, .к) ядляется функциональным аналогом ИМС ИР1, Микросхема КТ1 содержит четыре -двунаправленных переключателя (рис. 1,12, э), которые являются транзисторными бесконтактными аналогами электромеханических реле. При разрешающем потенциале на входе Е выводы X ч К микросхемы гальванически связаны через малое сопротивление открытых транзисторов. При этом X и К могут быть как входами, так и выходами ИМС. Логические элементы ИМС ЛА7-ЛА9. ЛЕ5, ЛЕ6 и ЛЕЮ, ЛИ1 и ЛП2, ЛП4, ЛП11 и ЛП12 имеют независимые входы. Микросхема ЛП1 содержит три элемента НЕ, из которых путем коммутации выводов можно получить элементы ЗИЛИ-НЕ или ЗИ-НЕ, -Шст 2-Ч 8 И--1 - д - л-

или 2ИЛИ-НЕ и НЕ. или 2И-НЦ и НЕ, или 2И я НЕ. или 2ИЛИ и НЕ. Оперативное ЗУ PMI является функциональным аналогом (т. е. структурные схемы и логика работы эквивалентны) ИМС 100РУ401 (см. рис. 1.2, л) и отличается от нее отсутствием инверсного выхода (выход 0). Два J К-тряггера TBI переключаются по входам У и У( по нарастающему перепаду С, а по входам /? и S - независимо от состояний входов /. К и С (рис. 1.11, з). Аналогично работают триггеры ИМС ТМ2, имеющие синхронизированный сигналом С вход D и иесиихроиизированиые входы R к S. Серия 170 [28, 30] состоит из ИМС АА1-АА4, АА6 и АА7, АП1-АП4, УЛ2, УЛ4, УЛ5, УЛ8-УЛП, УП1 и УШ, которые размещены в корпусах 201.14-1-201.14-9 и 238.16-2 и предназначены для построения устройств передачи данных в высокопроизводительных ЭВМ (ИМС АП1 и АП2, УП1 и УП2) и реализации усилителей записи и чтения в ЗУ (остальные ИМС). Например, сдвоенный формирователь импульсов тока АП1 и сдвоенный усилитель импульсов напряжения УП1 предназначены для работы с линиями связи, выполненными в виде пары проводников, и полностью совместимы с ТТЛ-схемами. Большое входное (для УП1) и выходное (для УП2) сопротивления мало нагружают линию передачи данных. Микросхемы АП2 и УП2 отличаются тем, что предназначены для работы с линиями связи большой емкости. Микросхемы АПЗ и АП4 являются формирователями сигналов для ЗУ на- МОП-элементах, работающих на большую емкость. Серия 176 [1, 10, 28] выпускается в корпусах 201.14-1 и 238.16-1 и лишь по некоторым конструктивным и электрическим параметрам незначительно отличается от серии 164 (см. табл. 1.4 и 1.II). Серия состоит из ИМС ИД1-ИД5, ИДЗ, ИД12 и ИД13, ИМ1, ИР2, ИРЗ и ИРЮ, КТ1, ЛА7-ЛА9, ЛЕ5, ЛЕ6 и ЛЕЮ, ЛИ1, ЛП1, ЛП2, ЛП4, ЛП11 и ЛП12, ЛС1, ПУ1-ПУЗ и ПУ5, РМ1, РУ2, TBI, ТМ1 и ТМ2, которые описаны в серии 164. Счетчик ИЕЗ (рис. 1.11, и) по модулю 6 имеет вход R установки в О и счетный вход Т. Состояния счетчика дешифрируются и выводятся в виде кода (а, Ь,..., g), удобного для управления 7-сегментным индикатором. Выводятся также дешифрованные 2-е и 6-е состояния счетчика. Выходы а, Ь,... g кроме того стробируются сигналом на входе С. Десятичный счетчик ИЕ4 отличается от счетчика ИЕЗ тем, что выводятся дешифрованные состояния 4 и 10. Назначение остальных выводов то же самое. Встроенный в ИМС ИЕЗ дешифратор позволяет дешифряровать и выводить все состояния десятичного счетчика (рис. 1.11, л). Запоминающее устройство РУ2 (рис. м) имеет два управляющих входа для задания типа операции (запись или чтение) и выбора МС, отсутствие возбуждающего сигнала на котором переводит выходы ИМС в высо-коомные состояния, что позволяет объединять выходы ИМС в монтажное ИЛИ. При этом выходы не более одной ИМС должны находиться в низко-омном состоянии. Серия 185 [24, 28] предназначена для построения ОЗУ (см. табл. 1.4) и сострит из ИМС РУ1-РУ5. Микросхема РУ1 (рис. 1.12, м) выпускается в корпусе 401.14-3 и содержит 16 запоминающих элементов (ЗЭ). Для выбора требуемой ячейки необходимо возбудить один из входов л, или Yf, При Ri = R = Si = = ~ 0 разряды слова из выбранной ячейки поступают на выходы ИМС. Для записи слова его разряды в парафазиом коде подаются на входы R и S 1-го и 2-го разрядов. Микросхемы РУ2 и РУЗ (рис. 1.L2; и) отличаются друг от друга быстродействием и некоторыми электрическими иа(5аметрами, размещены в корпусе 401.14-3 и содержат 64 ЗЭ. Обращение к ИМС возможно только при V = I. При этом R = S = О обеспечивает считывание, R = 5 = 0 - запись 1, а R = S = О - запись О по адресу, установленному на входах Л,. Микросхема РУ4 отличается от ИМС РУ2 и РУЗ корпусом (402.16-3), емкостью (256 бит) и, следовательно, числом входов Л,-(8), а также некоторыми электрическими параметрами. Емкость ИМС РУ5 равна 1 К одноразрядных слов, цикл 250 не, потребление 450 мВт от источника 5 В. Управляется РУ5 сигналами выбора

ООО «Мягкий Дом» - это Отечественный производитель мебели. Наша профильная продукция - это диваны еврокнижка. Каждый диван можем изготовить в соответствии с Вашими пожеланияи (размер, ткань и материал). Осуществляем бесплатную доставку и сборку. Звоните! Ежедневно! (926)274-88-54 Продажа и изготовление мебели. Копирование контента сайта запрещено. Авторские права защищаются адвокатской коллегией г. Москвы. |

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||