(926)274-88-54

Бесплатная доставка.

Бесплатная сборка.

График работы:

Ежедневно. С 8-00 до 20-00.

Почта: soft_hous@mail.ru

|

Звоните! (926)274-88-54 Бесплатная доставка. Бесплатная сборка. |

Ассортимент тканей График работы: Ежедневно. С 8-00 до 20-00. Почта: soft_hous@mail.ru |

|

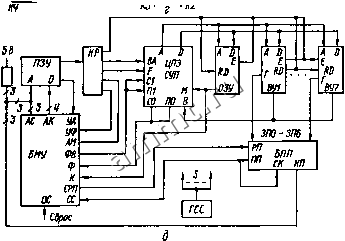

Читальный зал --> Особенности интегральных микросхем Многофункциональное устройство ХЛ4 выполняет функции делителя частоты с переменным коэффициентом деления, формирователя одиночных импульсов с заданной задержкой относительно стартовых импульсов или заданной длительностью и генератора серии с заданным числом импульсов. Состоит (рис. 1.29, в) из 4-разрядиого счетчика СТ, который управляется по D-входам блоком предустановки БП, генератора одиночных импульсов ГОИ и формирователей переноса ФП, импульсов ФИ деленной частоты, длительности ФД и серий ФС. Назначение выводов приведено в табл. 1.115. В режиме деления частоты V = \, С2 = СЗ = О, а иа вход С/ подают синхросигналы тактового питания. Запускается устройство путем подачи на вход РЗ сигнала произвольной длительности и фазы относительно тактового питания. ГОИ по сигналу с входа РЗ формирует синхронизированный тактовым питанием импульс начальной установки Таблица 1.И5 Номер вывода Назначение выводов ИМС 589ХЛ4 /, 3, 15 5, 10 6, 7 8, 16 9 11-14 Входы .синхросигналов С2, С1 и СЗ Вход V формирования длительности разрешения записи РЗ коэффициента пересчета счетчика Вход Р и выход С переноса счетчика Выходы формирователей длительности В и серий А импульсов Входы для подключения источника питания (О и 5 В соответственно) Выход F делителя частоты Входы D предустановки счетчика СТ по входам D, код на которых определяет коэффициент деления К = = 2 - /Сд, где п - число разрядов СТ; Кд, - код на входах D. После предустановки СТ начинает подсчет сигналов на С1. Первый сигнал на входе С1, который приходит после заполнения всех разрядов СТ единицами (код в СТ равен 11, ...1), вызывает появление на выходе F импульса, который по цепи обратной связи через БП осуществляет запись кода с входов D на СТ, обеспечивая тем самым заданный коэффициент пересчета. В режиме формирования длительности выход В соединяют со входом V. Сигнал на входе РЗ обеспечивает предустановку СТ по входам D и запуск формирователя длительности ФД, на выходе которого появляется сигнал 6=1, разрешаюищй по входу V подачу тактового питания иа вход СТ. Сигнал F = I, который генерирует ФИ после заполнения СТ, сбрасывает в исходное состояние ФД (В = 0). Так как сигнал В устанавливается по нарастанию С/, а сбрасывается по спаду, его длительность / определяется выражением /(д = 2 - (/ - т) /, где т - длительность сигнала С1, а / - частота. При этом на выходе А формируется серия из N импульсов, где N определяется по выражению /Сд= 2 - (Л - 1). Следует заметить, что задержка сигнала f = ! по отношению к сигналу начальной установки определяется выражением /(д = 2 - (4-т) / и может регулироваться установкой /Сд. Входы Р, С2 и СЗ и выход С используются для каскадирования ИМС с целью увеличения разрядности. На рис. 1.29, г показано соединение И.МС, работающих в режиме формировании сигнала заданной длительности. Описанные ИМС используют для построения процессоров микро-ЭВМ, параметры которых изменяются в широких пределах. Простейший процессор (рнс. 1.30, а) можно построить на основе ИМС только трех типов: ИК01, ИК02 и ПЗУ (например, К556РТ4). При этом разрядность обрабатываемых чисел изменяется в зависимости от числа использованных ИМС ИК02. Цикл выполнения МК начинается с ее выборки из ПЗУ. Для этого принятый по нарастанию 5 в РАМК адрес МК поступает на адресный вход ПЗУ МК. Выбранная по этому адресу МК с выхода ПЗУ поступает на управляющие входы БМУ и ЦПЭ, обеспечивая формирование адреса следующей МК в БМУ и выполнение данной МК в ЦПЭ. Результат выполнения данной МК поступает на входы одного из регистров ЦПЭ и выдается в виде признака СО или ПО в БМУ на вход Ф для ветвления микропрограмм и формирования сигналов С1 или П1. По спаду S указанный результат МК фиксируется на регистре ЦПЭ. По очередному нарастанию 5 подготовленный сигналами на входах УА, К а Ф адрес следующей МК фиксируется иа РАМК, начиная тем самым цикл выполнения новой МК. Таким образом, время Гц выполнения одной МК в процессоре состоит из времени прохождения сигнала по цепи от входа 5 до выхода адреса БМУ (30 не), времени t выборки МК из ПЗУ (70 не), времени выполнения операции в ЦПЭ, времени предустановки сигнала Ф на входе БМУ (15 не), времени Л записи результата в РОН при 5 = О (33 не). Время /ц зависит от числа ИМС ЦПЭ. В 16-разрядном процессоре их 8 и, следовательно, /ц равно времени прохождения сигнала от ШР к СО (43 не) в первом ЦПЭ и от СО к С1 (14 не) в семи остальных. Отсюда /ц > 43 -f 7 14 = 141 НС, а Го > 289 не, Время /ц можно значительно уменьшить, если использовать СУП (рис. 1.30, б). В этом случае /ц определяется временем прохождения сигнала от ШР к X н F (37 не), временем генерации сигналов переноса во все ЦПЭ (10 не) и временем предустановки CI относительно спада 5 (27 не). Кроме того, время предустановки сигнала Ф на входе БМУ становится некритичным (/б меньше времени предустановки С1 относительно спада S) и в Г не входит. Следовательно, /ц > 74 НС, а Го > 207 не. Длину ячеек ПЗУ выбирают, исходя из формата МК, который должен обеспечить управление всеми устройствами ЭВМ. Основная не зависящая от конфигурации ЭВМ часть МК должна содержать 7-разрядное поле управления адресом УА БМУ, 4-разрядное поле управления признаками УФ БМУ и 7-разрядное поле микрооперации F ЦПЭ. Дополнительная часть МК определяется структурой микро-ЭВМ и используемыми дополнительными устройствами и должна содержать не менее трех полей для задания маски ЦПЭ и управления ОЗУ и ЭВМ. Поле задания маски ЦПЭ по разрядности может совпадать с длиной обрабатываемых в ЦПЭ слов. Однако в большинстве случаев достаточно четырех разрядов, которые при К5, К4 = КЗ, К2 = К1, КО или при К5, К4 = - КЗ, К2, К1 = КО (рис. 1.30, г) обеспечивают подачу на ЦПЭ одной из двух групп масок: 0000 0001 OOFE OOFF 7F00 7F01 7FFE 7FFF 8000 8001 SOFE &9FF FFOO FFOl FFFE FFFF 0000 OOFF OfOO OFFF 7000 70FF 7f00 7FFF 8000 80fF 8f00 8FFF FOOO FOFF FFOO FFFF, заданных в системе с основанием 16, в которой F- 1111, £ = 1110. С помощью приведенных масок можно задавать константы О (О ООО) и 1 inn-P бирать младший разряд (0001) первого (FFOO) или второго (OOtF) байта; выделять знак (8000) или мантиссу (7FFF) числа. Поля МК, управляющие ОЗУ и УВВ, в простейшем случае должны содержать по два разряда, один из которых задает код операции (запись или чтение), а второй--разрешение обращения. Кроме того, дополнительная часть (55бт) л д SAC АН УА У9 БМУ <РВ (ИЩ) Ф /Г ±1 F А J) - Л- ЦПЭ м т С1 СО по От УВВ От ОЗУ Колонки о ) г 3 у

ЦПЭ - иПЗ - ЦПЭ - ЦПЭ - ЦПЭ - ЦПЭ - ЦПЗ - ЦПЭ к - к - к - к - к - к - к - К  Рнс. 1.30 МК может при необходимости содержать разряды для управления входами AM, ВА и ВД БМУ и ЦПЭ, а также другие необходимые для конкретной конфигурации микро-ЭВМ разряды. При решении какой-либо задачи на мнкро-ЭВЛ1 с рассмотренным процессором (рис. 1.30, а) необходимо составить и записать в ПЗУ микропрограмму ее решения. Процесс этот очень трудоемкий, так как даже простейшие арифметические операции, такие как умножение и деление, реа- лизуются rpcMos-iKHMH микроподпрограммами. В качестве примера рассмотрим деление без восстановления остатка положительных чисел X и Y, зафиксированных в R5 и R4 ссответственно. При этом предполагается, что X/Y = Z<\. Иначе необходимо было бы предусмотреть микроподпрограмму анализа переполнения. Микроалгоритм (МА) деления показан на рис. 1.31, а, его схемная интерпретация на рис. 1.29, б, а цифровая диаграмма деления числа Х= 0,01111 на число У = 0,11000 приведена >-J- о-вг НУ -- АС АС-1- АС КЗ* АС В5, АС СО- Z гб-I- HSAC ЯЗ. AC вг *AC*z -- AC. BI гУ-- B5*AC BS.AC CO Z В5-УАС R5,AC r- 7- BZAC-Z - A CO- С Г-8-  РП БПП Начало г 0-0 О вг с г 1- В2 + 1- В2 рц - АС АС1 АС ПЗУ Н в УА6 УАО J-SB Рис. 1.31 в табл. 1.116, в которой указаны состояния регистров R2, АС или R5 и выхода переноса СО после выполнения в t-м цикле (Ц) /-й МК (колонки Ц и В ). Деление начинается с установки Z в Ь и записи маркера (MR) в R2 (МКО и МК1), по которому в дальнейшем фиксируется конец операции деления. Далее осуществляется вычитание X - Y (МК2 - МК5) с целью получения первого остатка и цифры частного, относящейся к разряду целых. Указанная цифра генерируется в виде переноса СО, фиксируется в триггере Z и однозначно определяет знак нового остатка. Действя-тельно, при выполнении деления в такте сложения в знаковый разряд сумматора поступает либо О (знак положительного остатка) и Ь (знак Таблица 1.116

-У), либо 1 (знак отрицательного остатка) и О (знак -{-У). Следовательно, СО = О свидетельствует, что новый остаток отрицательный (О ! = 1 н переноса нет), а С(? = 1 свидетельствует, что новый остаток положительный (единица в знаковом разряде суммы перешла в О , вследствие чего возник перенос). МК6 осуществляет сдвиг остатка Q на один разряд влево путе.ч выполнения операции Q -j- Q = 2Q. МК7 и МК8 осуществляют сдвиг кода в R2 влево на один разряд и запись в младший разряд сформированной ранее МК5 очередной цифры частного. Прн выполнении МК8 анализируется перенос СО. Сигнал СО = I означает, что MR прошел все разряды R2 и, следовательно, деление закончено. При СО = О осуществляется переход на новый цикл, а знак выполняемой операции определяется анализом состояния Z. При Z = О к остатку прибавляется прямой, а при Z = ! - обратный код делителя. При размещении МК в ПЗУ необходимо учитывать особенности формирования адреса следующей МК в БМУ, которые состоят в следующем: нулевая строка ПЗУ отличается от других строк тем, что к ее ячейкам можно перейти с помощью МК JZR из любой ячейки ПЗУ, вследствие чего ее ячейки следует расходовать экономно; условные переходы по F, С, Z осуществляются только к колонкам 2 и 3 или 10 и 11, вследствие этого МК с указанными переходами при распределении ячеек ПЗУ следует размещать в первую очередь, а проверки условий чередовать с вычислительными МК, что позволяет сократить число невычислительных МК, осуществляющих только проверку условий; плотность размещения МК повышается, если в зоне расположения микропрограмм отсутствуют незаполненные ячейки. Микропрограмма деления, записанная в символической форме и размещенная в ячейках ПЗУ с учетом указанных особенностей, приведена в табл. 1.117. Наглядность размещения МК в ПЗУ повышается, если использовать графическую модель ПЗУ в виде 16 ко- лонок по 32 ячейки (рис. 1.30, в), в каждой из которых указывается номер хранящейся в ней МК. Значительно сократить трудоемкость программирования на уровне МК можно путем введения второго (командного) уровня программирования. Одна из основных задач, возникающих при этом,- выбор системы команд. Два противоположных решения этой задачи состоят в следующем. В первом случае система команд выбирается с учетом эффектявной реализации алгоритмов задач, которые будут решаться на проектируемой ЭВМ. Ориентация на класс решаемых задач существенно повышает эффективность ЭВМ, однако программная несовместимость разрабатываемой ЭВМ с существующими рядами ЭВМ создает значительные трудности в создании как сервисных, так и прикладных программ. Во втором случае разрабатываемая ЭВМ реализует одну из известных систем команд, например Таблица 1.117

ЕС или СМ ЭВМ, что позволяет значительно сократить затраты на программирование за счет использования созданного для этих ЭВМ программного обеспечения. При выборе структуры команд аппаратура накладывает некоторые ограничения. Например, код операции команды целесообразно представлять 8-разрядным полем, так как именно такую часть команды БМУ может принять за одни такт по шине К. Применение более длинного кода операции приводит к миоготактной расшифровке адреса первой МК микропрограммы, которая соответствует даииой операции. Это, в свою очередь, замедляет вычислительный процесс. Общая длина команды определяется длиной обрабатываемых слов, которая равна удвоенному числу используемых секций ЦПЭ. Применение более длинных команд требует многократного обращения к ОЗУ в цикле выборки команды, что также замедляет вычислительный процесс. Особенности схемных решений при 2-уровневом управлении рассмотрим на примере одноадресной ЭВМ с 16-разрядным процессором (рис. 1.30, д), которая состоит нз восьми ЦПЭ со схемой ускоренного переноса СУП, ПЗУ емкостью 512 слов, оперативного ЗУ емкостью не более 64 К слов, семи внешних уст ройств ВУ1 - ВУ7, БМУ, блока приоритетного прерывания БЛП и конвейерного регистра КР. Применение последнего позволяет почти в два раза сократить цикл выполнения МК за счет совмещения выборки последующей МК с выполнением очередной. В этом случае выбранная по сформированному в БМУ адресу МК разбивается иа две части. Первая часть МК поступает на входы УА БМУ для формирования адреса следующей г; J? фиксируется на КР и управляет работой остальных Р выборке из ПЗУ i-й МК в ЦПЭ выполняется I - IMK, а в БМУ формируется адрес для выборки i -f- I МК. Такая организация вычислительного процесса возможна только в том случае, если результат i-й МК не влияет иа адрес ( + 1)-й МК. Такое влияние

ООО «Мягкий Дом» - это Отечественный производитель мебели. Наша профильная продукция - это диваны еврокнижка. Каждый диван можем изготовить в соответствии с Вашими пожеланияи (размер, ткань и материал). Осуществляем бесплатную доставку и сборку. Звоните! Ежедневно! (926)274-88-54 Продажа и изготовление мебели. Копирование контента сайта запрещено. Авторские права защищаются адвокатской коллегией г. Москвы. |

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||