(926)274-88-54

Бесплатная доставка.

Бесплатная сборка.

График работы:

Ежедневно. С 8-00 до 20-00.

Почта: soft_hous@mail.ru

|

Звоните! (926)274-88-54 Бесплатная доставка. Бесплатная сборка. |

Ассортимент тканей График работы: Ежедневно. С 8-00 до 20-00. Почта: soft_hous@mail.ru |

|

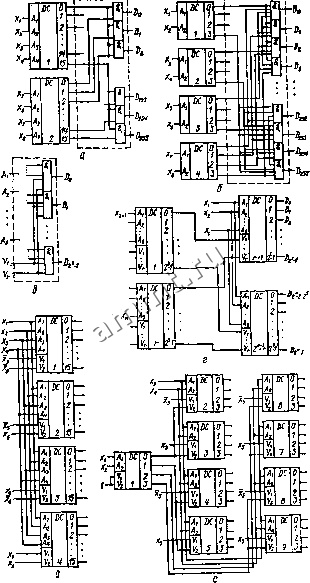

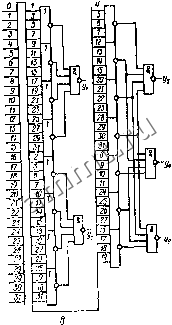

Читальный зал --> Особенности интегральных микросхем Наращиваемость ПЛМ по k достигается за счет использования разрв шающего входа V (рис. 2.9, б) или путем объединения выходов ПЛМ монтажным ИЛИ . Каждую из функций fi-ft можно представить в виде fi = = ф1 (xv Xi, Хз) V % (xi, Xi, Xf), ( = 1,2, 3, 4), a каждую из функций U - h - как = ф2 (Xl, Xi, Хз) V (х*> Xi, Xg), (j = 5, 6, 7, 8). При этом функции ф1 и фл реализуются на PLM1, а функции и г)у - соответственно иа PLM2 и PLM3. В зависимости от конкретного вида функций fi-fg в наборы аргумеитои функций ф и if могут входить и повторяющиеся аргумеи- Таблица 2.13 ф 1 1 1 - - 1 Xi 0.1-101 Х5 10 - 011 г. г* О 1 О О ООО 1 1 О 1 1 О О О 1 ты. Вторая возможность иаращиваиия ПЛМ по fe используется в различны вариантах (рис. 2.9, в), где /i и /2 - функции трех аргументов х, Xj, х,; и и /в - функции также трех аргументов Х4, Х5, х,; /з и /4 - функции шести аргументов Xj. Х2.....х причем /3 = фз (xj, Xj, Х3) V Фз (. 4. *в); f* = = Ф4 (Jfi. Xt. Хз) V 4 ( 4. Xi, Xj). Функции ф Ф4 и ij-s, Ф4 рвализуются соответствеиио иа PLM1 и PLM2. Такой вариант соответствует наращиванию как по k, так и по п (рис. 2.9, г). Если для используемых ПЛМ fe = 8, то для реализации функции f, представленной дизъюнкцией более чем восьми элементарных произведений, необходимо объединять выходы ПЛМ. При использовании нескольких ПЛМ для удобства их программирования все функции, содержащие некоторое число повторяющихся элементарных произведений, целесообразно реализовать с помощью одной и той же ИМС даже в том случае, когда на входы всех ПЛМ поданы одинаковые переменные. Наращиваемость ПЛМ по параметру т обеспечивается параллельным подключением нескольких ПЛМ к одним и тем же входным цепям (как показано иа втором каскаде рнс. 2.9, 6 или г). Проектирование типовых комбинационных устройств к устройствам комбинационного типа, используемым в цифровой технике, относятся дешифраторы, преобразователи кодов, сумматоры, шифраторы, схемы сравнения чисел и др. Поэтому с инженерной точки зрения представляют интерес не только общие методы проектирования комбинационных устройств, но и частные функционально и структурно-ориентированные, учитывающие особенности комбинационных устройств, обусловленные как видом реализуемых функций, так и возможиостямя используемых ИМС [27, 29]. Дешифраторы иа интегральных МС. В общем случае функционирование полного дешифратора можно описать системой из 2 функций Do W = Х1Х2Х3 . . . х ,х ; D2n-2 W - Х1Х2Х3 . . . x iX ; Dn-i W = X1X2X3 . . . x ,x . Если фуикциоиироваиие дешифратора, имеющего п входов, описывается менее, чем 2 функциями, то такой дешифратор называют неполным. Как указывалось ранее, система функций (X), (j = О, 1, .... 2 - 1) является совокупностью всех возможных конституент единицы от п переменных. При использовании ИМС малой степени интеграции задача проектирования дешифратора сводится к представлению функций (X) в операторной форме, если выполнено условие п < М, где М - коэффициент объединения ИМС по входу. Например, для элементов И-НЕ и ИЛИ-НЕ при п = 4 можно записать Do = XiXiXgXi = Xl У Xi у Хз у Xi; Di = Х1Х2ХзХ4 = Xi V . 2 V *з V Xi, Dj = XiXaX24 = Xi\/ ХзУхзУ Xi; D3 = XiX2X3X4 = Xl V *2 V 3 V 4 и T. Д. При n> M применяют каскадное соединение дешифраторов, каждый нз которых дешифрирует группу входных переменных, число которых не превышает Л1. Такой способ построения дешифраторов наиболее распространен в цифровой технике, а изложенная ниже методика проектирования дешифраторов обеспечивает минимальную сложность и максимальное быстродействие. Прн наличии ИМС с М < п входные переменные разбивают на М групп по ]пШ1 или ]п/М - 1[ переменных, где запись вида ]п/М[ означает округление в сторону ближайшего большего целого числа, если п/М - дробное или же само п/М, если п/М - целое. При таком разбненнн может оказаться, что для некоторых групп переменных ]п/М1 > М или ]п/М - -1[ > М. Эти группы, в свою очередь, разбивают на М подгрупп с равными или отличающимися на единицу количествами переменных. Такое разбиение продолжают до тех пор, пока не получат группы с М илн меньшим числом переменных. На всех каскадах дешифратора, начиная с последнего (выходного), входные переменные необходимо группировать так, чтобы полностью использовать входы логически элементов. Неиспользуемые входы элементов допускаются только на первом каскаде (естественно, их должно быть как можно меньше). Например, при п = 8; М = 4 для дешифратора по схеме на рис. 2.10, а требуется 288 элементов. Однако такой дешифратор не является оптимальным, так как у элементов второго каскада используются лишь два входа. Вместе с тем дешифратор на рис. 2.10, б. у которого входные переменные разбиты на четыре группы, при том же быстродействии содержит на 16 элементов меньше. Быстродействие оптимального дешифратора характеризуется максимальной задержкой сигналов в его каскадах, составляющей т]1о§д,п[, где  ч - задержка сигналов одним функциональным элементом. Точную оценку сложности оптимального дешифратора (по числу функциональных элементов) дать трудно. Однако при конкретных значениях л и Л1 это можно сделать, воспользовавшись формулой L(n, M) = 2 +S L(n,. М), Рнс. 2.10 где л,- -целые числа, удовлетворяющие условию П( = п. Сумма L {til, Щ имеет наименьшее значение, когда Л; принимают i=i блнжайшне к п/М значения, т. е. л/ п/М. Тогда } L(л, М) = 2 + MSr* +ML (п/М\ М). Отсюда получаем L (л, М) 2 -f MS + МП * + УИ32П/Л1 + ... Дешифраторы на определенное число выходов можно выполнить как ИМС повышенной степени интеграции (см. рнс. 2.4, а). В таких ИМС должны быть предусмотрены возможности наращивания их структуры путем каскадного подключения других ИМС (одна нз таких возможностей показана на рис. 2.5). Выполнение требования наращиваемости означает, что дешифратор л-разрядных слов можно построить на основе ИМС-дешифраторов для s-разрядных слов (л > s) без каких-либо изменений во внутренней структуре последних. Прн этом распределения m выводов ИМС - дешифратора на входы и выходы должны быть такими, чтобы общее число И.МС для дешифратора л-разрядных слов было минимальным. В общем случае внутренняя структура ИМС - дешифратора, удовлетворяющего требованию наращиваемости, показана на рнс. 2.10, в, где входы Лх.Лз, As - информационные; входы Vi, Vj, Vr - управляющие. Значение s в этом случае выбирают максимально возможным прн данном т, но таким, чтобы выполнялись условия r = m s-2 ; 1</-<2+1. Для реализации дешифратора на л входов нз набора однотипных ИМС-дешнфраторов применяют многокаскадную схему (рис. 2.10, г). К управляющим входам каждой нз ИМС DC (г + 1), DC (г -f 2), DC (2 ~ -f + г) подключено по одному выходу от каждого дешифратора DC1, DC2, DCr, причем наборы выходов дешифраторов, подключенных к ИМС, не повторяются. Принцип построения дешифраторов DC1, DC2, DCr аналогичен. Рассмотрим конкретные примеры. Пусть т = 22; л = б, тогда S = 4; г = 2. Такой дешифратор можно построить с помощью одного каскада модулей (рнс. 2.10, д). На рнс. 2.10, е показан дешифратор на пять входов, построенный на модулях с /л = 8; s = 2; г = 2. Рассмотрим особенности проектирования неполных дешифраторов на примере зна- коного индикатора, в котором для свечения одного нз символов 0,1.....9 необходимо подать единичный сигнал по одной из десяти шин. Будем считать, что индицируемые символы представлены в коде с весами 8, 4, 2, 1. Следовательно, дешифратор должен реализовать лишь 10 функций Dg, D,... D четырех аргументов Xi, х, Jc ж*- О- Прн этом шесть наборов таких аргу- -р Im ментовюю, ЮН, П00.П01, пю. ПИ jDj: р ПТ* являются избыточными. Это можно ис- J JLJ пользовать для упрощения реалнза- j. t:: Ш>.</ цни тех функций DjiX), которые ЩаГ* принимают единичное значение на наборах, соседних с избыточными (на рнс. 2.И, а избыточные наборы отмечены 1 В/  Рнс. 2. И Ркс. 2.12 прочерками). Таким образом, операторные формы функций Dj (Х) для элементов И-НЕ и ИЛИ-НЕ имеют вид: Dj = .,Хз4 = Xi\J Xj \/ Xt; D,i = х-3:з4 = Н V 3 V -<4; D = xxXi = V 3 V *4; Dj = хх-Л = Xj V лз V 4; Dj = xXi = Xj V 3 V - 4; D, = X2X3X4 = Xj V V J4; Dg = XiXj = Xl V 4; 224 De = X1X4 = Xl V 4- Схема неполного дешифратора знакового индикатора изображена на рнс. 2.11, б. Неполные дешифраторы на JV < 2 выходов на основе ИМС-дешифраторов получить очень просто: строят полный дешифратор на 2 выходов, а затем используют лишь те нз ннх, которые соответствуют заданным функциям Dj (Х). Проектирование шифраторов. Шифратором называют комбинационное устройство, имеющее k входов, п выходов и выполняющее функции, обратные функциям дешифратора, т. е. преобразующее единичный сигнал на одном нз k входов (унитарный fe-разрядный код) в двузначный код номера этого входа. Если выходной код имеет естественный порядок весов числа 2, то я = Jlogj k[. Метод построения функциональной схемы шифратора очень прост. Если номеру / входа шифратора, на котором присутствует единичный сигнал, соответствует двузначный выходной код С, то /-ю входною цепь необходимо подвести ко входам элементов ИЛИ в тех выходных разрядах, где Cj содержит единицы. Пусть fe = 10 н выходной код имеет естественный порядок двоичных весов. Тогда п = 4, а систему функций, реализуемых шифратором, можно записать как 1/1= \ \/ 3 У 5 У 7 \/ 9; Уз = = 2V3V6\/7; r/8 = 4V5\/6V7; у=8У9. Цифры в правой части этих выражений соответствуют номерам входов шифратора. Схема такого шифратора показана на рис. 2.12, а, а его условное обозначение - на рнс. 2.12, б. Когда коэффициент объединения по входу М используемых ИМС меньше fe/2, целесообразно проектировать каскадные шифраторы. Один нз методов каскадного построения шифраторов состоит в следующем. Вначале формируют дизъюнкции по М входных цепей, коды номеров которых имеют единицу в первом (младшем) разряде, затем формируют дизъюнкции по М входных шнн, коды номеров которых Cj имеют единицу во втором разряде н т. д. Элементы, реализующие эти дизъюнкции, составляют первый каскад шифратора. Во втором н всех последующих каскадах формируют дизъюнкции по М функций предыдущего каскада, соответствующих единице в первом разряде С., затем во втором разряде С - и т. д. Общее число k каскадов составляет При таком построеннн шифратора на каждом г-м каскаде (г= 1, 2, 3, ...) некоторые днзъюикцнн по М функций предыдущего каскада будут общими для выходных функций ys, y i.....уп, где s> logj -f 1. Например, fe = 32; M = 4, тогда 5,1 = (1 V 3 V 5 V-7) V (9 V И V 13 V 15) V (17 V 19 V 21 V 23) V V (25 V 27 V 29 V 31); f/, = (2 V 3 V 6 V 7) V (10 V 11 V 14 V 15) V (18 V 19 V 22 V 23) V V (26 V 27 V 30 V 31); (/3 = (4 V 5 V 6 V 7) V (12 V 13 V 14 V 15)- Y (20 V 21 V 22 V 23) V V (28 V 29 V 30 V 31); (2.13) (/4 = (8 V 9 V 10 V 11) V (12 V 13 V 14 V 15) V (24 V 25 V 26 V 27) V V (28 V 29 V 30 V 31); i(5 = (16 V 17 V 18 V 19) V (20 V 21 V 22 V 23) V (24 V 25 V 26 V 27) V V (28 V 29 V 30 V 31). Из этих выражений видно, что дизъюнкция (12 V 13 V 14 V 15) является общей для функций и у, дизъюнкция (20 V 21 V 22 V 23) - для 8 e-2ua 225

ООО «Мягкий Дом» - это Отечественный производитель мебели. Наша профильная продукция - это диваны еврокнижка. Каждый диван можем изготовить в соответствии с Вашими пожеланияи (размер, ткань и материал). Осуществляем бесплатную доставку и сборку. Звоните! Ежедневно! (926)274-88-54 Продажа и изготовление мебели. Копирование контента сайта запрещено. Авторские права защищаются адвокатской коллегией г. Москвы. |