(926)274-88-54

Бесплатная доставка.

Бесплатная сборка.

График работы:

Ежедневно. С 8-00 до 20-00.

Почта: soft_hous@mail.ru

|

Звоните! (926)274-88-54 Бесплатная доставка. Бесплатная сборка. |

Ассортимент тканей График работы: Ежедневно. С 8-00 до 20-00. Почта: soft_hous@mail.ru |

|

Читальный зал --> Особенности интегральных микросхем Поле 2 Содержанке операции 0000 0001 0010 ООП 0100 0101 0111 Пояснения РД РД Pi (0-7) = == РД (8-15) ±\ +РД +РД Pi (0-7) = = РД (8-15) РД+ 1

Ha ША выдается код О, содержимое ЗУ А не изменяется На ША выдается содержимое регистра Р{ ЗУ А, номер которого указан в РИ, после чего содержимое Pi при X = 1 (вывод 6) увеличивается на 1 ША : = РД. Р{ : = Р( + 1 Pi:= Pi-\ Pi := Pi + РД На ША выдается код, первый байт которого взят из Pi (разряды 0-7), а второй - из РД (разряды 8-15). Указанный код увеличивается иа 1 и записывается в Pi Pi:= РД+1 При X = О Й/Л : = Pi и Р( : = = Р, + I, а при X = 1 ШЛ : = = РД и Р.- = РД + 1 При X = О ШЛ : = Р,- и Pj : = = Р; 4- О, а при X = \ША : = Д и Pi : = Р,- + 1 При X = О ШЛ : = Pf и Р, =. = Р( - 1, а при X = 1 МК выполняется аналогично МК ОНО Триггер блокировки прерывания сбрасывается в О Триггер блокировки прерывания устанавливается в 1 Состояние ИМС и ее выходов не изменяется Временные параметры ИМС 583ИК1 Таблица 1.58 Время: действия сигнала S3 = О опроса (запрета) tn (ti) сигналом S3 информации на выходах ШД, ША и / Задержка сигналов на выходах ШД, ША и / относительно спада S2 при разрешающем значении S3 <250

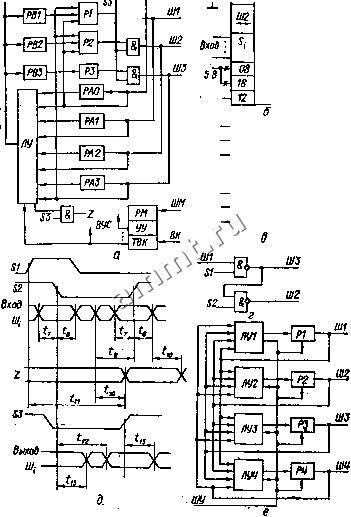

Рис. 1.21 является управляющим словом УС устройства управления и поступает на операционную часть ЭВМ, которая генерирует признаки П : X и I, используемые для ветвления микропрограмм. Р° У ИК1 можно использовать для построения механизмов дресации данных. Она обеспечивает прямую, относительную, присое-дниенную и косвенную адресации как с инкрементацией (прибавлением 1), так 9 dts иее. Для реализации механизма адресации необходимо путем коммутации выводов ИМС обеспечить подачу адресной части команды на ШД, а индексной и управляющей частей - на ШМ соответственно на 2,3 и О, 1, 4-7 разряды. Например, для реализации прямой адресации с ннкре-ментадией можно воспользоваться МК, представленной на рнс. 1.20, е. Коммутационный МП КП1 предназначен для построения коммутаторов и буферных устройств хранения данных. Его можно использовать для построения мажоритарной восстанавливающей схемы в системах с трехкратным резервированием. ИМС состоит (рис. 1,21, а) нз 12 8-разрядных регистров {РО-РЗ, РАО-РАЗ н РВО-РВЗ), логического ЛУ н управляющего УУ Таблица 1.59 Номер вывода Назначение выводов ИМС ШКП1 б, 6, 8-13 И, / , 2, 28. 32, 15, 19, 23, 29, 33, 37, 41, 46 16, 20, 26, 30, 34, 38, 42, 45 17, 21, 27, 31, 35, 39, 43, 44 24 25 и 48 Входы синхросигналов приема S1 и выполнения S2 МК н выдачи информации Выход Z признака нуля Шины МК ШМ, номера разрядов которых образуют ряд 3, 2, 7, 6, 1, О, 4 и 5 Вход сигнала выбора кристалла ВК Двунаправленная шина ШЗ Двунаправленная шина Ш2 Двунаправленная шина Ш1 Двунаправленная шина ШО Шина нулевого потенциала Выводы для подключения источника пнтання Таблица 1.60

устройств с регистром МК РМ. Обмен информацией осуществляется по четырви двунаправленным шинам ШО-ШЗ, шине МК н неоднородной управляющей шине (табл. 1.59). Выдача информации на ШО-ШЗ возможна только с соответствующих регистров РО-РЗ при разрешающем потенциале иа входе S3. Управляет работой ИМС 8-разрядная МК, состоящая из двух нввавййнмых полей 1 и 2. Поле 2 (разряды МКб и МК7) задает одну нз четырех функций. Которые выполняются над операндами в ЛУ (табл. 1.60), а адреса операндов и остальные функции ЛУ задает поле 1 (табл. 1.61). Как и в ос-тальньГх ИМС 583 серии по нарастанню S1 МК н ВК фиксируются на РМ и триггере ВК ТВК- Если ВК = О, то МК не выполняется, содержимое РА и РВ сохраняется, а иа выходах Z и Ш0-Ш1 устанавливаются нули. После дешифрации команды спад S2 фиксирует информацию на (t = = 0,3), вследствие чего она при разрешающем потенциале на S3 выдается иа lUi. После выполнения МК по нарастанню S2 производится занесение 10 11 12 13 14 15

10 0 0 3 10 0 1 10 10 10 11 6 110 0 о о 1 1 1 1 1110 0 1 Над содержимым PAI PBJ : = PAI (ЛУ) РАЗ PBJ : = Ш1 (ЛУ) ШЗ и PAJ выполняется логическая операция, определенная полем 2 МК- Результат заносится в PBJ. Номера 1 м J указаны соответственно в разрядах 2 и .3, 4 н 5 МК. Если результат равен нулю, то Z = 1. В противном случае и во всех остальных МК Z = О ШЗ : = PBJ. Содержимое PBJ записывается в PJ, который управляет ШЗ. Поле 2 для этой н последующих МК не влияет на результат PBJ : = /л (ШС, ШД, ШЕ). Над кодами с трех различных шин (СФ Д-ф Е Ф 1) выполняется поразрядная мажоритарная операция функция /а нз табл. 1.1) .>ДС : = РВД : = РВЕ : = U (ШС, ШД, ШЕ). МК4 выполняются аналогично МКЗ, но результат заносится в трн разных регистра РВ. J указывает шину и регистр РВ, которые в операции не участвуют ШС : = РВС, ШД : = РВД, ШЕ : = РВЕ. На три разных шины выдаются коды с соответствующих им регистров РВ (С ф Д ф Е = J) РВС : = РВД : = РВЕ : = f (РАС, РАД, РАЕ). МК6 выполняется аналогично МК4, но данные поступают с трех разных регистров РА РАЗ : = ШЗ. В РАЗ записывается код о ШЗ PAi : = Ш1. На все PAi принимаются коды о Д/. (1 = 0,3) Д/i : = PBj. На все Д/; выдаются коды с РВ ((.= 0.3). Ш1 Ш1 Ш1 Ш1 Ш2 Ш2 = ШО, = ШЗ, = ШО = ШЗ = ШО = ШЗ Ш2 : = ШЗ. Ш2 : = ШО. Коммутация шни информации в PAi н РД,-. Временная диаграмма работы МС КП1 показана на рнс. 1.21, д, а временные характеристики - в табл. 1.62 (параметры 4, h-k ИМС КП1 определяются аналогично соответствующим параметрам ИМС ВМ1 н равны друг другу). МП КП1 обеспечивает прием информации с шнн данных в регистры и выдачу данных с регистров в шины, коммутацию шин, логическую обработку сайтов, последовательный прием н одновременную выдачу до четырех байтов данных, параллельный прием и выдачу четырехбайтных данных, сравнение байтов с выдачей признака их равенства (операция aft V я* и г = 1) и поразрядное мажорирование данных с трех шин или регистров с записью результата в одни нлн трн регистра. Временные параметры ИМС 583КП1 t{. НС Время: предустаиойки /7~н удержания ig данных на входах Ш0~ШЗ > 100 относительно спада S2 (МК коммутации) или нарастания S2 (МК записи информации в РА) предустановки i данных иа входах ШО-ШЗ при МК записи информации в РВ 150 Задержка: сигнала Z t относительно сигналов на входах ШО-ШЗ при < 300 разрешающем S3 сигнала Z tn относительно нарастания S1 при разрешаю- < 400 щем S3 сигналов tii на выходах ЩО-ШЗ относительно спада S2 < 250 сигналов иа выходах ШО-ШЗ относительно Sg < 150 Таблица 1.63 Номер вывода Назначение выводов ИМС 583ВА1 1-4. 22-24 б. п. 16. 21 6, 10. 16. 20 7, 9, 17. 19 8. 18 J2 Синхросигналы Sj, S, S 5 , 5* и Sg Двунаправленнан шина Ш2 с открытым коллектором Ш1 с открытым коллектором ШЗ с повышенной нагрузоч- ной способностью и выходным каскадом типа эмиттер-ного повторителя (открытый эмиттер) Выводы для подключения источников питания Шина нулевого потенциала Двунаправленный вывод А признака ошибки (открытый эмнттер) Двунаправленный вывод К контрольного разряда (открытый эмнттер) Таблица 1М

Магистральный приемопередатчик ВА1 предназначен для коммутации информации между двумя типовыми (для серии 583) шинами Ш1 и Ш2 и шиной ШЗ с повышенной нагрузочной способностью (табл. 1.63). Он состоит (рис. 1.20, г) из двух регистров Р1 и Р2 и схемы контроля СК. ИМС выполняет девять элементарных МК (табл. 1.64) в зависимости от комбинации сигналов на входах (t = 1.7). На остальных наборах сигналов МК либо вообще не выполняется, либо выполняется суперпозиция элементарных МК-Наппимеп, при всех 5 = 1 ни одна нз МК не выполняется, а прн всех Si - О выполняются МК1. МК2 и МК5. а именно: Ш:= Р1 М Р2 Ш1 \J V Ш2 Одновременно с выдачей информации на ШЗ выдаются контрольные разряда: KA+Xa+Xi+Kg+Xg (mod2) и Л = /С + Д/3 (0) + Д/, (1) + -f Д/з (2) + Шg (3) (mod 2). где Xi - цифра в t-м разряде Ш1 или Р1 при передаче информации с Ш1 илн Р1, либо цифра в г-м разряде Ш2 ли Р2 при передаче с Ш2 или Р2\ ШЗ (i) - цифра в i-u разряде ШЗ (1 = 0,3). Формирование по таному правилу сигналов Л и Л в сочетании с двунаправленными выводами позволяет передаваемую на ШЗ информацию сопровождать контрольным разрядом К, сформированным по четности (Л = 1) или нечетности (Л = 0); при приёме информации с ШЗ контролировать по сигналу Л число единиц в коде и увеличивать разрядность путем каскадирования. Временные параметры ИМС характеризуются задержками распространения сигналов в Ш1, Ш2 и ШЗ 100 не), сигналов /С 150 не) и Л 75 НС) относительно сигналов 8/. Соединение выходов ИМС при каскадировании для увеличения разрядности показано на рис. 1.20, е. ВА1 можно использовать в качестве усилителей сигналов (например, синхроимпульсов), так как она допускает по выводам МЗ соединение с линией длиной до 65 м (рис. 1.21, б). Магистральный приемопередатчик ВА2 предназначен для коммутации двух типовых для 583-й серии шин Ш1 (входная) и Ш2 (выходная с открытым коллектором) с двунаправленной шиной ШЗ с повышенной нагрузочной способностью и открытым эмиттером (рис. 1.21, в). Он состоит из пяти изолированных друг от друга спаренных схем И-НЕ (рнс. 1.21, г). При S1 - = 1 ШЗ: - Ш1 и при S2 = 1 эта же информация передается на Ш2. Прн St = 82= 1 информация с ШЗ передается на Ш2. Наименьшая задержка в ИМС составляет 20 не (цепь Ш1-ШЗ), а наибольшая - 35 не. Магистральный коммутатор ХЛ1 предназначен для коммутации четырех типовых для 583-й серии шнн, логической обработки байтов и построения мажоритарных восстанавливающих схем в системах с трехкратным резервированием. Он состоит из четырех идентичных каналов, каждый из которых включает 8-разрядное логическое устройство ЛУ и регистр Р,- (t = 1,4) с двунаправленной шиной (ШО данных (рис. 1.21, е). Управляется ХЛ1 сигналами на шине управления ШУ, состоящей из двух общих для всех каналов сигналов /? н S(, и четырех независимых групп сигналов S, S.g, 5,з (i = = 1,4), каждая из которых управляет t-м каналом (табл. 1.65). В зависимости от значения сигналов S, 8ц, 82, -S.j i-e ЛУ позволяет выполнять 12 разно- табл. 1.1. Перечень всех разновидностей выполняемых ЛУ операций приведен в табл. 1.66. Например, если необходимо выполнить поразрядную конъюнкцию байтов с Ш1 и Ш2 н результат направить на ШЗ и Ш4, то это м HaTvv/- = = IOO- Р этом на ЛУ/ н ЛУ2 подают сигналы, обеспечивающие выдачу на Ш1 и Ш2 vnLu/ P 12 < о) = (Sai, Sm, Ss, S ) = 0010. Если это >ииовие не выполнено, то на входы ЛУЗ и ЛУ4 подают коды, полученные путем поразрядной дизъюнкции от данных с Р/ и шины Ш1, на которую

ООО «Мягкий Дом» - это Отечественный производитель мебели. Наша профильная продукция - это диваны еврокнижка. Каждый диван можем изготовить в соответствии с Вашими пожеланияи (размер, ткань и материал). Осуществляем бесплатную доставку и сборку. Звоните! Ежедневно! (926)274-88-54 Продажа и изготовление мебели. Копирование контента сайта запрещено. Авторские права защищаются адвокатской коллегией г. Москвы. |

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||