(926)274-88-54

Бесплатная доставка.

Бесплатная сборка.

График работы:

Ежедневно. С 8-00 до 20-00.

Почта: soft_hous@mail.ru

|

Звоните! (926)274-88-54 Бесплатная доставка. Бесплатная сборка. |

Ассортимент тканей График работы: Ежедневно. С 8-00 до 20-00. Почта: soft_hous@mail.ru |

|

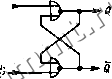

Читальный зал --> Полупроводниковая схемотехнология ся ВЫСОКООМНЫМ, можно с успехом использовать при мультиплексировании сигналов. Однако такая схема имеет существенный недостаток: переход в высокоомное (единичное) состояние из-за паразитных емкостей происходит всегда медленнее, чем в низкоомное (нулевое). Поэтому вместо элементов с открытым коллектором лучше использовать элементы с трехстабильным вшодом. Они содержат обычный двухтактный выходной каскад, который, одна-10, может быть переведен в особое высо-тмное состояние безразличного выхода . Для управления выходным каскадом служит специальный вывод-разрешение выдачи данных. Соответствующая схема ТТЛ представлена на рис. 9.23. Если уровень управляющего напряжения Ue низкий, запираются оба транзистора 7 и Т. При высоком уровне Ue получим обычную логическую связь И-НЕ между входными сигналами и, и U2. Аналогичным образом можно перевести в высокоомное (безразличное) состояние и трехстабильный элемент КМОП. 9.5. ИНТЕГРАЛЬНЫЕ ТРИГГЕРЫ Помимо логических элементов, реализующих основные логические функции, большое значение в качестве базовых элементов цифровой техники имеют различные триггерные схемы, работа которых будет описана также с помощью основных логических функций. Это дает возможность понять принцип их действия независимо от используемой в каждом случае схемной реализации. 9.5.1. ОСНОВНАЯ СХЕМА Триггер можно получить, охватив, как показано на рис. 9.24, два логических элемента ИЛИ-НЕ обратными связями. Он  имеет два выходных сигнала: Q я Q, инверсные друг другу, и два входных: S (установка-Set) и R (сброс-Reset). Если входные сигналы взаимоинверсны, причем S = 1 и R = О, то Q = sTQ = TTQ = О, e=R-i-e = o + o=i. Следовательно, оба выходных сигнала действительно находятся в инверсных друг Таблица 9.13 Таблица переключений RS-Tpnrrepa

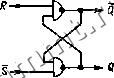

другу состояниях. При R = 1 и S = о можно получить обратные значения выходных сигналов триггера. Если R = S = О, состояние выходных сигналов сохраняется. Поэтому RS-триггер можно использовать  Рис. 9.24. KS-триггер на элементах ИЛИ-НЕ. Рис. 9.25. RS-триггер на элементах И-НЕ. для запоминания информации. При R = = S = 1 оба выходных сигнала равны нулю; однако в этом случае состояние выходных сигналов триггера не будет определено, если в какой-либо момент оба входных сигнала одновременно станут равными нулю. Поэтому комбинация входных сигналов R = S = 1, как правило, является запрещенной. Все возможные состояния триггера отображены в таблице переключений 9.13. Мы уже ознакомились с этой таблицей, изучая транзисторную схему на рис. 8.8. В разд. 9.2 было отмечено, что логическое тождество не изменяется, если все переменные инвертировагь, а операции ( + ) и ( ) поменять местами. Используя это Таблица 9.14 Таблица переключений RS-Tpnrrepa на элементах И-НЕ

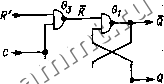

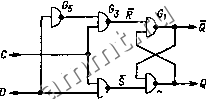

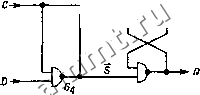

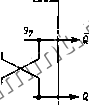

правило, можно получить RS-триггер, построенный на элементах И-НЕ (рис. 9.25), с таблицей переключений 9.13. Следует, однако, обратить внимание на то, что в качестве входных сигналов используются переменные Л и S. Так как мы часто будем рассматривать Л-триггер на элементах И-НЕ, для входных переменных R и S представлена еще одна таблица переключений 9.14. Статический синхронный RS-триггер Часто необходим такой триггер, который реагировал бы на входные сигналы только в определенные моменты времени. Эти моменты задаются с помощью дополнительного входного сигнала синхронизации С. На рис. 9.26 показан такой статический синхронный RS-триггер. При С = О сигналы Л = S = 1. В этом случае триггер запоминает предыдущее состояние. При С= 1 R = R, S = S  Рис. 9.26. Статический синхронный RS-триггер. И эта схема ведет себя как обычный RS-триггер. Статический синхронный D-триггер Рассмотрим далее, как с помощью триггера, изображенного на рис. 9.26, можно запомнить значение логической пере-  в4 г Рис. 9.27. Статический синхронный D-триггер.  Рис. 9.28. Упрощенная минающего устройства. схема ячейки запо- менной D. Ранее было показано, что Q = = S, если входные сигналы инверсны друг другу и С = 1. Следовательно, для того чтобы запомнить значение переменной Д нужно лишь положить S = D и R = D, Для этого на рис. 9.27 используется инвертор G5. В выполненной таким образом ячейке памяти во время такта С = 1 устанавливается Q = D. Если С = О, то запоминается полученное состояние триггера Характерная особенность запоминающей ячейки состоит в том, что она имеет только один информационный вход D. Эти схемы называются обычно О-триггерами. Легко заметить, что элемент G4 на рис. 9.27 при С = 1 работает как инвертор для переменной D. Поэтому можно исключить инвертор G5 и получить при этом упрощенную схему запоминающей ячейки, представленную на рис. 9.28. 9.5.2. ТРИГГЕРЫ ТИПА M-S (MASTER-SLAVE) Статический синхронный триггер реагирует на входные сигналы в течение всего времени, пока тактовый сигнал С равен единице. Часто, однако, вместо этого триггера необходим такой, в котором считываемая информация не передавалась бы не- Триггер с двумя бистабильными ячейками, одна из которых является ведущей, а другая ведомой.-Яр л . ред. Рис. 9.29. Л5-триггер типа M-S. .6/ а. Ведущий  Ведомый тередственно на выход, а появлялась там только тогда, когда входы схемы уже заперты. Это требование можно удовлетворить с помощью схем, работающих по принципу ведущий-ведомый . На рис. 9.29 изображены два статических синхронных RS-триггера, которые стробируются одним штовым сигналом С, причем на вход второго триггера этот сигнал подается в про-тавофазе. Для инвертирования такта служит элемент Gg. Рассмотрим функционирование этой схемы с помощью изображенной на рис, 9.30 временной диаграммы тактового импульса С. Если напряжение тактового импульса превосходит уровень а, то ведомый триггер отключен от ведущего. При возрастании напряжения до уровня b в ведущий триггер запишется информация, поданная на вход. Очевидно, что безупречная работа схемы достигается только тогда, когда обеспечивается именно эта последовательность событий. В противном слу- Ркс. 9.30. Уровни срабатывания триггера типа M-S, чае входная информация поступает прямо на выход схемы без промежуточного запоминания в. ведущем триггере. Чтобы воспрепятствовать этому, порог срабатывания для логической единицы в инверторе G, делают ниже, чем в элементах И-НЕ G и Gj, При достижении уровня с ведущий триггер снова отключится от входов схемы. И наконец, при достижении уровня d информация перепишется в ведомый триггер и установится на выходах. Следовательно, изменение состояния выходов этой схемы возможно только по отрицательному фронту тактирующего импульса. Так как ведущий триггер повторяет состояние входов схемь! в течение всего времени, пока с равно единице, на выход ведомого триггера передается только тот входной сигнал, который имел место непосредственно перед отрицательным фронтом тактового импульса. В отличие от ранее рассмотренных статических триггеров триггер типа M-S с помоидью обратных связей можно использовать в качестве делителей частотьь Для этого полагают S = ё и R = е, благодаря чему выходной сигнал меняется на инверсный при каждом отрицательном фронте тактового импульса (счетный триггер). Как видно из рис. 9.31, при этом на выходе схемы появляются прямоугольные Рис. 9.31. Временная диаграмма триггера типа M-S при введении обратной связи R = Q и S = = Q (счетный триггер). импульсы, частота которых равна половине тактовой частоты. Если такими же обратными связями охватить статический триггер, то при С = 1 возникнут высокочастотные автоколебания. Действительно, в этом случае из-за незапертых входов схемы ее состояние по ис-

ООО «Мягкий Дом» - это Отечественный производитель мебели. Наша профильная продукция - это диваны еврокнижка. Каждый диван можем изготовить в соответствии с Вашими пожеланияи (размер, ткань и материал). Осуществляем бесплатную доставку и сборку. Звоните! Ежедневно! (926)274-88-54 Продажа и изготовление мебели. Копирование контента сайта запрещено. Авторские права защищаются адвокатской коллегией г. Москвы. |