(926)274-88-54

Бесплатная доставка.

Бесплатная сборка.

График работы:

Ежедневно. С 8-00 до 20-00.

Почта: soft_hous@mail.ru

|

Звоните! (926)274-88-54 Бесплатная доставка. Бесплатная сборка. |

Ассортимент тканей График работы: Ежедневно. С 8-00 до 20-00. Почта: soft_hous@mail.ru |

|

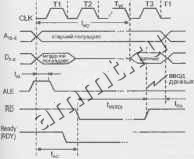

Читальный зал --> База цифровых устройств -OXj L -сгЬ -OXj 5 Bo-с 470 5B&- Выуод Ф1Ф2 Рис. 5.7. Внешние элементы тактсесгс генератора (а) и формирование синхросигналов (б) в микропроцессоре K1821BM85A Для образования сигналов синхронизации CLK выход генератора подается на вход счетного триггера (рис. 5.7, (5). Триггер формирует две последовательности противофазных импульсов Ф1 и Ф2 для тактирования внутренних схем МП. Сигнал синхронизации системы CLK синфазен импульсам Ф2. Сигнал ALE формируется как один импульс последовательности Ф1, вьще-ляемый из псе в первом такте (Т1) каждото машинного цикла. Буфер вьшачи сигнала ALE во внешние цепи имеет вход разрешения EN. Частота синхросигналов МП в два раза ниже частоты генератора. Синхронизация и последовательность действий МП Командный цикл КЦ (рис. 5.S, о) начинается с выборки коматтды (Opcode Fetch, OF). Первый машинный цикл Ml всегда OF, в нем МП получаст первый байт команды. После этого могут быть еше один или два машинных цикла типа MR (Memory Read), поскольку команда может быть однобайтной, двухбайтной и.П1 трехбайтной. Если команда трехбайтная, то она хранится в памяти так, как показано на рис. 5.8, 6. Первый байт содержит кодоперации КОП. сведения о способе щресапии, а если команда однобайтная, то и адрес операнда. Наличие адре- са возможно для операций типа регистр-регистр с короткими адресами Для адресации S регистров общего назначения достаточны трехразрядные адреса, а для адресации регистровых пар даже двухразрядные. Второй байт содержит младщий полуадрес операнда, если команда трехбайтная, или непосредственный операнд либо адрес ВУ, если команда двухбайтная. Третий байт содержит старщий полуадрес операнда или байт непосредственных данных при загрузке пары регистров. Адреса регистров и регистровых пар даны в табл. 5.2.

Рис. 5.в. Циклы и такты микропроцессора К1821ВМ85А (а) и пример размещения команды в памяти микропроцессорной системы (б) Таблица 5.2

После выборки и декодирования команды могут понадобиться дополнительные мащинные циклы для ее выполнения. Всего в командном цикле может быть от одного до пяти машинных циклов. Машинный цикл состоит из тактов, в которых выполняются типовые действия, рассмотренные ниже. Число тактов в различных машинных циклах - 3...6. Больщинство машинных циклов содержат три такта, В командном цикле может содержаться от 4 до 18 тактов. Сигналы, реализующие тот или иной МЦ, генерируются блоком управления МП на остювании информации, содержащейся в первом байте команды Проиллюстрируем сказанное примером вьшолнения команды 5ТАЬзЬ2 (Store Accumulator Direct), передающей содержимое аккумулятора в ячейку памяти при прямой адресации, т. е. указании адреса ячейки в самой команде. Команда трехбайтная, для ее передачи в МП требуются три машинных цикла, в первом из которых байт bi передается в регистр команд IR, в последующих байты Ьз и Ьз передаются в регистры временного хранения W и Z. После получения всей команды МП выполняет ее передавая байт из аккумулятора в ячейку памяти; адрес которой поступил в МП Таким образом, цикл команды составится из четырех машинных циклов в следуюшем ею-рядке OF-MR-MR-MW. Каждый машинный цикл делится на такты (состояния) - интервалы между одноименными фронтами тактовых импульсов.   Рис. 5.9. Временные диаграммы цикла чтения микропроцессора Типовые действия, выполняемые в тактах машинного цикла: Т. Адрес памяти или ВУ выставляется на AD7 o и Ajs-g, генерируется сигнал ALE для фиксации битов AD7 o. На линиях Ю/М, S] и So выстав)ы-ется информация, определяюшая тип цикла. Проверяется флаг HALT. Т2 Проверяются входы Ready и Hold. Программный счетчик ипкременти-руеггся, если данный машинный цикл есть часть выборки команды. Во всех машинных циклах кроме цикла BI (освобождения шин) один из управляющих стробов RD, WR или FNTA переходит из единичного состояния в активное нулевое. Т Появляется при неготовности памяти или ВУ к обмену (на линии READY низкий уровень напряжения). Состояния линий адресов, данных и управления остаются теми же, что и в конце такта. Сигнал READY проверяется в каждом такте ожидания. Байт команды или данных передается в микропроцессор или из него. Уровень активного управляющего строба изменяется с нулевого на единичный.

ООО «Мягкий Дом» - это Отечественный производитель мебели. Наша профильная продукция - это диваны еврокнижка. Каждый диван можем изготовить в соответствии с Вашими пожеланияи (размер, ткань и материал). Осуществляем бесплатную доставку и сборку. Звоните! Ежедневно! (926)274-88-54 Продажа и изготовление мебели. Копирование контента сайта запрещено. Авторские права защищаются адвокатской коллегией г. Москвы. |

|||||||||||||||||||||||||||||||||||||||||||||||