(926)274-88-54

Бесплатная доставка.

Бесплатная сборка.

График работы:

Ежедневно. С 8-00 до 20-00.

Почта: soft_hous@mail.ru

|

Звоните! (926)274-88-54 Бесплатная доставка. Бесплатная сборка. |

Ассортимент тканей График работы: Ежедневно. С 8-00 до 20-00. Почта: soft_hous@mail.ru |

|

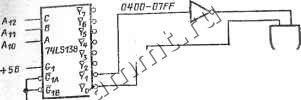

Читальный зал --> Отладка микропроцессорных систем Двоичный код на четырех входных линиях вызывает на одной из 16 выходных линий изменение пассивного состояния логической 1 на активное состояние логического О, если два разрешающих входа Gi и G2 находятся в активных состояниях. Если, например, работа микросхемы разрешена сигналами Gi и G2 и на входы подан двоичный код 0000, то выход Уо окажется в активном состоянии логического О , а все остальные выходы останутся в пассивных состояниях логической 1 . На рис. 1.11 дешифратором 74154 управляет сигнал запроса памяти MRQ, входящий в шину управления. Данный рисунок показывает систему с ВВ, отображенным на ВВ, так как срабатывание логики выбора микросхем формирует сигнал запроса памяти; аналогичный дешифратор необходим и для выбора портов ВВ, но с заменой сигнала запроса памяти на сигнал запроса ВВ. В системе с ВВ, отображенным на память, работа микросхем памяти и ВВ должна разрешаться от общего дешифратора адреса, который либо должен быть постоянно разрешен путем подключения его разрешающих входов на землю и к источнику злектропитания, либо должен разрешаться каким-либо синхронизирующим сигналом от микропроцессора. Схему, приведенную на ряс. 1.11, можно модифицировать для системы с отобра-жением на память, подключив вход Gi к питанию -Ь5 В, а вход G2-на землю. Во многих небольших системах, например, в специализированных промышленных контроллерах, не требуется использовать все имеющееся адресное пространство. Сигналы выбора блоков могут потребоваться на границах, меньших адресных границ 4К, показанных на рис. 1.11. Если существующие требования можно удовлетворить при наличии памяти меньше 16К и применить микросхемы с емкостью 1К, схему на рис. 1.11 следует изменить, подав на входы дешифратора 74154 линии адреса Лю-Л13. От дешифратора получается 16 выходов на границах 1К, а младшие 10 линий адреса Aq- Лд подаются на все микросхемы памяти 1К. В небольших системах часто применяется дешифратор 74LS138 с тремя входами и восемью выходами. Рис. 1.12 показывает адресное пространство 8К, дешифрируемое по границам 1К. Здесь с помощью линий адреса 10. Ац и Ai2 формируются 8 сигналов разрешения бло- OVDO-DiFF = З-вмдпВый дешифратор С е Вышами Ао~Ад У  Схеиа опре -деления только счигпь1~ вания

Шина данных Рис. 1.12. Пространство памяти 8К, дешифрируемое по адресным границам 1К КОВ ПО 1К. Отметим, что в данной схеме сигнал разрешения работы ПЗУ (СЕ) обусловлен управляющим сигналом RIW, чтобы предотвратить возникновение конфликта на шине. При соответствующем выборе дешифраторов адреса и линий адреса можно разделить пространство памяти на блоки любого размера. Если применяемые микросхемы памяти имеют организацию, меньшую формата слова компьютера, их следует включить параллельно с образованием блока памяти, ширина которого равна требуемому формату слова. Микросхема ЗУПВ 2114 (рис. 1.13) имеет внутреннюю организацию 1024X4, поэтому для получения памяти с байтной структурой две такие микросхемы следует включить параллельно. Младшие линии адреса и управляющие сигналы подаются в микросхемы параллельно, но шина данных расщеплена между ними. Младшие четыре линии шины данных Го-Оз подключены к одному ЗУПВ, а старшие четыре линии Di-Bj- ко второму ЗУПВ. Когда в ЗУПВ записывается байт данных, младшая тетрада (четыре бита) записывается в ЗУПВ а старшая тетрада - в ЗУПВг. Аналогично считывание из ЗУПВ вызывает считывание старшей тетрады из ЗУПВг, а младшей тетрады -- из ЗУПВ1. Восьмибитный микропроцессор выдает сразу байт дан- От дгш.афра-/пора адреса Иикро-скепа Zm Макрв- {шч)тв2 Шина ванных (1}о~Щ} Рис. 1.13. Параллельное включение микросхем памяти ПЫХ и полагает, что ЗУПВ является байтной микросхе-мой. Такие же рассуждения относятся и к микросхемам памяти с организацией ЫУ(,1, но для образования блока памяти с байтной структурой потребуется включить параллельно восемь микросхем. 1.6. Микроконтроллер Микроконтроллер представляет собой устройство на основе микрокомпьютера, которое используется для решения задач управления и измерения. Программа его специализирована на выполнение ограниченного числа конкретных функций, например, на считывание сигналов преобразователей, обработку значений данных и выдачу управляющих сигналов. Требование знергонеза-висимой памяти, предопределяет размещение программы в ПЗУ, а для хранения промежуточных данных предусматривается небольшое ЗУПВ. Микроконтроллеры отличаются от компьютеров общего назначения в основном относительным использованием ПЗУ и ЗУПВ. В машине общего назначения требуется большое ЗУПВ, так как выполняемые ею программы часто заменяются, а для этого необходимо ЗУПВ, и в то же время требуется небольшое ПЗУ для хранения часто используемых фиксированных программ. Микроконтроллер же имеет относительно большое ПЗУ для.хранения своих фиксирован ных программ и небольшое ЗУПВ для стека и временного хранения данных. В микроконтроллере требуется

ООО «Мягкий Дом» - это Отечественный производитель мебели. Наша профильная продукция - это диваны еврокнижка. Каждый диван можем изготовить в соответствии с Вашими пожеланияи (размер, ткань и материал). Осуществляем бесплатную доставку и сборку. Звоните! Ежедневно! (926)274-88-54 Продажа и изготовление мебели. Копирование контента сайта запрещено. Авторские права защищаются адвокатской коллегией г. Москвы. |

|||||||||||||||||