(926)274-88-54

Бесплатная доставка.

Бесплатная сборка.

График работы:

Ежедневно. С 8-00 до 20-00.

Почта: soft_hous@mail.ru

|

Звоните! (926)274-88-54 Бесплатная доставка. Бесплатная сборка. |

Ассортимент тканей График работы: Ежедневно. С 8-00 до 20-00. Почта: soft_hous@mail.ru |

|

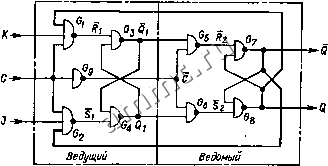

Читальный зал --> Полупроводниковая схемотехнология  Рис. 9.32. JiC-триггер тапа M-S. течении времени задержки будет меняться на обратное. Если входные элементы И-НЕ Gi и Gj имеют дополнительные входы, то из счетного триггера получается JX-триггер типа M-S, изображенный на рис. 9.32. При J = = К = 1 происходит описанное выше изменение состояния триггера во время каждого отрицательного фронта тактовых импульсов. Таблица переключений JX-тригге-ра 9.14 совпадает с таблицей переключений RS-триггера, а именно J действует как вход установки, а Х-как вход сброса. Единственное различие возникает при за-прешенной комбинации входных сигналов R = S =1. Описывая действия JX-триггера, необходимо сделать одно сушественное допущение, учитывающее действие обратной связи: таблица переключений 9.15 верна только тогда, когда состояние JX-входов не изменяется, пока тактовый импульс С равен единице. Действительно, в отличие от RS-триггера типа M-S на рис. 9.29 ведущий триггер в данном случае может быть J = J J К = К -К опрокинут только один раз и не вернется i г-- в прежнее состояние, поскольку один из Благодаря этому часто можно экономить-его двух входных элементов И-НЕ всегда внешние логические элементы. С помощью Таблица 9.15 Таблица переключений Ж-трнггера типа M-S. (Изменение выходного сигнала происходит в момент появления отрицательного фронта тактового импульса) блокирован сигналом обратной связи. Если не учитывать это ограничение, то ошибки при построении цифровых схем будут неизбежны! Имеются специальные JX-триггеры типа M-S, в которых этот недостаток отсутствует. В таких триггерах, снабженных блокировкой информации, записывается именно то состояние входов, которое имело место в момент появления положительного фронта тактового импульса. Непосредственно после этого фронта оба входных элемента блокируются и больше не реагируют на изменения сигналов на входах. Другая возможность решения этой проблемы состоит в использовании динамических триггеров. Большинство выпускаемых в интегральном исполнении JX-триггеров имеет несколько J- и Х-входов. Они действуют точно так же, как и описанный выше триггер, если учесть, что

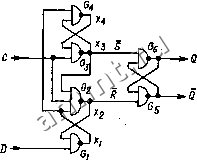

С-D- Pit 9.33. Превращение JK-триггера в Х)-триг-Ч лополнительных выводов триггер устана-швается в определенное состояние неза-исимо от тактового импульса. Эти вы-юды называются входами предустановки 1 стирания. Таблица 9.16 Таблица переключений D-триггера Если перед входом К включить инвертор, как показано на рис. 9.33, то получится D-триггер типа M-S. Его таблица переключений 9.16 представлена ниже. 9.5.3. ДИНАМИЧЕСКИЙ ТРИГГЕР Триггер, в котором отсутствует сквозная передача сигнала с входа на вьеход, также можно получить, блокируя входы в тот момент, когда считываемая информация передается на выход. Подобные аемы называются триггерами с динамическим воздействием по входу синхронизации или просто динамическими триггерами. При этом различают два типа таких триггеров: триггеры, в которых передача информации происходит на положительном фронте тактового импульса, и триггеры, в которых передача информации осуществляется на отрицательном фронте этого импульса. Среди этих триггеров наиболее распространен D-триггер, однако имеются и JK-триггеры такого типа. На рис. 9.34 показана структура D-триг-гера, управляемого положительным фронтом. Если сигнал С равен нулю, то всегда Xj = Хз = 1. При этом выходной триггер Cs/Gj работает в режиме хранения информации. Прием информации со входов схемы в оба вспомогательных триггера Gj/Gj и G3/G4 происходит совершенно иначе, чем в двухступенчатом триггере. Пока С = О, xi = D, Х4,= Xi = D. х2 = х3 = 1 и Это означает, что всегда в одном из двух вспомогательных триггеров оба выходных сигнала равны единице. Это неправильное состояние исчезает, когда тактовый сигнал С примет единичное значение. Устанавливающийся при этом выходной сигнал определяется другим вспомогательным триггером, находящимся в правильном состоянии. Из этого следует при D = 0: Хз остается в 1, Хг переходит в 0; при D = 1: Хз остается в 1, Хз переходит в 0. Сигнал, принимающий нулевое значение.  Рис. 9.34. Динамический D-триггер. и определяет состояние оконечного триггера, т.е. во время появления положительного фронта тактирующего импульса выполняется равенство: Q = D. Рассмотрим теперь, как производится последующее запирание входов данной схемы. Мы видели, что после передачи информации оба вспомогательных триггера находятся в правильном состоянии. Но в этом случае они блокируют друг друга, так что все последующие изменения сигнала D не вызывают никакой реакции: при х2 = О заблокирован и, следовательно, Xj, х4 = const; при Хз = О заблокированы G2 и G4 и, следовательно, х2, х4 = const. Рис. 9.35. Действие тактового импульса на динамический триггер. Рис. 9.36. Динамический D-триггер как делитель частоты. Рис. 9.37. Временная диаграмма делителя частоты. Новая информация запишется только тогда, когда при С = О один из двух вспомогательных триггеров перейдет в неправильное состояние. В заключение рассмотрим функционирование этой схемы, пользуясь рис. 9.35. Когда величина сигнала С превысит уровень а, входной сигнал будет воспринят и передан на выход схемы. Если информация на входе и изменится непосредственно после приема, то все равно состояние выходного триггере останется неизменным. На основе этого свойства динамический триггер можно использовать в качестве делителя частоты, применив для этого, как и ранее, обратную связь. С этой целью, как показано на рис. 9.36, на вход D подают сигнал Q. Временная диаграмма работы такой схемы изображена на рис. 9.37. 9.6. ПОЛУПРОВОДНИКОВЫЕ ЗАПОМИНАЮЩИЕ УСТРОЙСТВА 9.6.1. ОПЕРАТИВНЫЕ ЗАПОМИНАЮЩИЕ УСТРОЙСТВА (ОЗУ) ОЗУ представляет собой запоминающее устройство, в котором при подаче адреса какого-либо слова может производиться запоминание или считывание ин- формации по этому адресу (с про-извольным доступом). Из технологически! соображений отдельные ячейки памяти располагаются не по одной линии, а Kai бы образуют квадратную матриц; (рис. 9.38). При обращении к определенно! ячейке пам,яти на соответствующие гори зонтальную и вертикальную шины подается логическая единица. С этой целью заданный вектор адреса а = ( ...а ) следует декодировать соответствующим образом Для этого служат дешифраторы столбцов и строк, которые представляют собой обычные дешифраторы один из и *. Помимо адресных входов в ОЗУ имеет ся один информацио1шый вход D , инфор мационный выход D,, вход разрешенш записи WE (Write Enable) и вход выбора микросхемы С5 (Chip Select), называемый иногда входом доступа к микросхеме С1\ (Chip Enable). Последний вход служит дм организации мультиплексной работы нескольких микросхем ОЗУ, передающих информацию на общую шину даниы! (J3C7S-System). Если CS = О, то информа ционный выход Dbhx переходит в высо-i коомное состояние и не влияет на передачу информации по шине данных. Для того чтобы осуществить такое подключение, информационный выход должен быть выполнен в виде либо элемента с открытым коллектором, либо трехстабильного элемента. При разрешении записи {WE = 1) выходной элемент также переводится в высокоомное состояние с помощью соответствующей логической связи. Этим достигается воз.можность соединения выводов и Dbux, что позволяет осуществить передачу данных в обоих направлениях (иа запись и на считывание) по одному проводу (двунаправленная шина данных). С помощью еще одного логического элемента запрещается переход схемы в состояние запись , когда CS = 0. Благодари этому предотвращается ошибочная запись информации в микросхему, пока она не будет выбрана для занссе1П)я информации, На рис. 9.38 отображены все указанные логические связи. Схема гюдключения каж- В оригинале допущена не точность, ш как в данном случае каждьп! дешифратор выбирает один из 2 * h>.-Прим. перев.

ООО «Мягкий Дом» - это Отечественный производитель мебели. Наша профильная продукция - это диваны еврокнижка. Каждый диван можем изготовить в соответствии с Вашими пожеланияи (размер, ткань и материал). Осуществляем бесплатную доставку и сборку. Звоните! Ежедневно! (926)274-88-54 Продажа и изготовление мебели. Копирование контента сайта запрещено. Авторские права защищаются адвокатской коллегией г. Москвы. |