(926)274-88-54

Бесплатная доставка.

Бесплатная сборка.

График работы:

Ежедневно. С 8-00 до 20-00.

Почта: soft_hous@mail.ru

|

Звоните! (926)274-88-54 Бесплатная доставка. Бесплатная сборка. |

Ассортимент тканей График работы: Ежедневно. С 8-00 до 20-00. Почта: soft_hous@mail.ru |

|

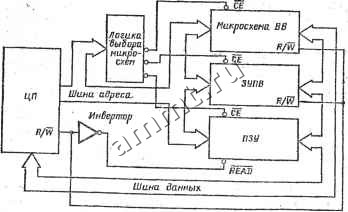

Читальный зал --> Отладка микропроцессорных систем НИИ в высокоимпедансное состояние, либо разрешает им выдать двоичные уровни на те линии, к которым они подключены. Обычно в микропроцессорной системе управляющие сигналы подчиняются стандарту негативной логики, что отмечается чертой отрицания над мнемоникой сигнала. Активным значением таких сигналов является нулевой потенциал, поэтому, например, микросхема памяти может выдать данные на шину данных, когда ее вход СЕ имеет состояние логического О . В пассивном состоянии ЦП переводит все микросхемы, подключенные к шине данных, в высокоимпедансное состояние, так что ни одна из них не может выдать данные на шину. Когда же ЦП осуществляет считывание из ячейки памяти или входного порта, он селективно разрешает работу только соответствующей микросхеме, оставляя все остальные схемы запрещенными. Выбранная микросхема помещает данные на шину, с которой их считывает ЦП. После этого ЦП запрещает работу выбранной микросхемы, возвра щая шину в пассивное состояние. Управление передачами информации в компьютере обеспечивается тем, что ЦП селективно разрешает выдать данные на шину данных только О.ВДОЙ микросхеме. Это справедливо и для драйверов шины данных самого ЦП. 1.5. Дешифрирование адреса В типичной вычислительной системе для хранения программ и временного хранения данных используется большое число микросхем памяти. Кроме того, имеется несколько входных и выходных портов .цля взаимодействия с внешними устройствами. ЦП должен селективно разрешать работу каждой микросхеме памяти, вхо.цно-му или выходному порту, когда они должны воспринимать данные с шины .цанных или помещать данные на нее. Сам ЦП не может сформировать от.цельные выбирающие (селектирующие) сигналы для каждой из микросхем, имеющихся в системе. Выбирающие сигналы необхо.цимо вьщелить из информации на шине а.цреса и сопроводить их соответствующими сигналами шины управления. Обычно компоненты, применяемые в микрокомпьютерах, не содержат по одной ячейке памяти или от.цельно-му входному или выходному порту. Микросхемы памяти организованы в блоки из 1К ячеек и имеют внутренний ешифратор, обеспечивающий доступ к отдельным ячейкам Типичная микросхема памяти содержит 1К, 2К или 4К байтных ячеек, а выбор конкретной ячейки осущест-> вляет внутренний дешифратор по состояниям линий шины адреса. К микросхеме 1К непосредственно подключаются 10 младших линий адреса Aq-Ад, определяющих конкретную ячейку. Конечно, имеются исключения из общего правила, когда емкость микросхемы меньше 1К или ее ячейки имеют меньше 8 бит. Общий принцип выбора микросхем остается тем же самым, а изменяются только детали подключений, которые и учитывают тип применяемых микросхем. В малых или дешевых системах применяются отдельные входные и выходные порты, что требует однозначного дешифрования их адресов по информации на шине адреса. Для упрощения схем дешифраторов портам обычно присваивается блок адресов памяти, и любой из этих адресов разрешает работу порта. Однако в настоящее время заметна тенденция использовать в микрокомпьютерах программируемые микросхемы ВВ, в которых имеются несколько ячеек, предназначенных для выполнения функций ВВ, и внутренний дешифратор для выбора конкретной ячейки. Старшие линии адреса служат для генерирования сигналов СЕ. выбирающих микросхемы памяти и ВВ. Рис. 1.7 иллюстрирует механизм расщепления шины адреса  Рис 1.7. Упрощенная схема дешифрирования адреса между микросхемами памяти и ВВ, а также логику выбора микросхем. Младшие линии адреса подключены непосредственно ко всем блокам системы, а старшие линии адреса поданы в логическую схему выбора (де. шифратор). Для обращения к конкретной ячейке в системе используется весь двоичный код на шине адреса; младшие линии определяют ячейку внутри блока адресов, а старшие линии- блок адресов. При таком способе адресации микросхему можно разместить где угодно в общем пространстве памяти, а ее точное местонахождение определяется соединением входа СЕ с соответствующим выходом логики выбора микросхем. В микропроцессорных системах применяются два вида полупроводниковой памяти. Запоминающие устройства с произвольной выборкой (ЗУПВ) выполняют операции записи и считывания, а из постоянного запоминающего устройства (ПЗУ) микропроцессор может только считывать информацию. ПЗУ являются знергонезави-симыми, т. е. их содержимое сохраняется при отключении злектропитания, а ЗУПВ знергозависимы. ПЗУ применяются для хранения программ в таких системах, где неудобно загружать программу после каждого выключения питания. К подобного рода системам относится большинство приборных и управляющих систем. Для предотвращения конфликтов на шине разрешение работы ПЗУ часто обусловлено сигналом шины управления, который идентифицирует операцию считывания. На рис. 1.7 сигнал шины управления, определяющий операции считывания или записи, показан с мнемоникой R/W. Она обозначает, что операция считывания задается уровнем логической 1 на линии R/W, а операция записи - уровнем логического 0. Большинство сигналов разрешения микросхем имеют активный низкий уровень, т. е. сигнал истинен при уровне логического О, поэтому до , подачи сигнала R/W в ПЗУ его необходимо инвертировать. На схемах сигналы с активным низким уровнем показываются с кружком в местах входов и выходов (см. вход READ в ПЗУ на рис. 1.7). В микросхемах ЗУПВ управляющий сигнал R/W, определяющий тип выполняемой операции, подается непосредственно на соответствующий вход. Если в линии R/W присутствует уровень логического О, когда работа микросхемы разрешена низким уровнем сигнала

ООО «Мягкий Дом» - это Отечественный производитель мебели. Наша профильная продукция - это диваны еврокнижка. Каждый диван можем изготовить в соответствии с Вашими пожеланияи (размер, ткань и материал). Осуществляем бесплатную доставку и сборку. Звоните! Ежедневно! (926)274-88-54 Продажа и изготовление мебели. Копирование контента сайта запрещено. Авторские права защищаются адвокатской коллегией г. Москвы. |