(926)274-88-54

Бесплатная доставка.

Бесплатная сборка.

График работы:

Ежедневно. С 8-00 до 20-00.

Почта: soft_hous@mail.ru

|

Звоните! (926)274-88-54 Бесплатная доставка. Бесплатная сборка. |

Ассортимент тканей График работы: Ежедневно. С 8-00 до 20-00. Почта: soft_hous@mail.ru |

|

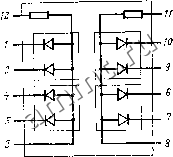

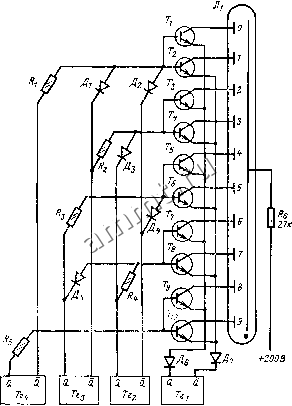

Читальный зал --> Цифровые измерительные приборы Рассмотрим для примера работу дешифратора при индикация цифры 3 На выходах Q триггеров Тг\ и Тгг высокий потенциал, на выходах 5 -низкий Диод Дз заперт; с выхода Q триггера Тгз ток через резистор Rt течет в базу транзистора Г4 и отпирает его. Транзистор Гз при этом заперт, так как его эмиттер подключен к выходу Q триггера Tzi, имеющему высокий потенциал. Диоды Дй и Д7 обеспечивают isannpa-ние неработающих транзисторов. В некоторых случаях диоды схем совпадения могут быть заменены на резисторы. Подобная схема дешифратора приведена на рис. 16. Потенциалы на выходах триггеров могут быть нулевыми или отрицательными. Отрицательный потенциал, снимаемый с триггера Тги составляет около 0,5 В, с триггеров TZi-Tzi-8-10 В. Базы транзисторов дешифратора подключены к источнику -Ь6 В через  Рис. 14. Интегральная схема К2ЛП173. резисторы Pi4-и к выходам триггеров через резисторы R\-Рю. Для включения какого-либо из ключевых транзисторов необходимо, чтобы на плечах триггеров, к которым подключена через резисторы база данного транзистора, был нулевой потенциал. Отношение сопротивлений резисторов R\-Rw и Rn-Rn выбрано таким, что если хотя бы на одном из упомянутых плеч триггера имеется отрицательный потенциал, то соответствующий транзистор будет заперт Рассмотрим, как происходит индикация цифры 3 Код этой цифры ООП, что соответствует потенциалу порядка - 0,5 В на эмиттере транзистора Га, нулевому - на эмиттере транзистора Т\ и на выходе триггера Тг и порядка -8 В на выходах Q триггера Тг и триг- Таблица 6 Состояния входов и выходов десятичного дешифратора

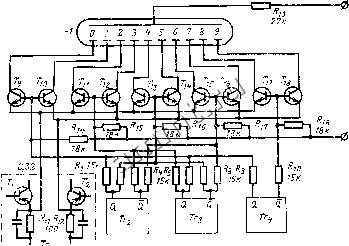

геров Тгз и Тг . На нижних выводах резисторов и Rr, нулевой потенциал, что обеспечивает возможность включения транзисторов Т\\ и Т\2, в рассматриваемом случае включится транзистор Г2, так как потенциал его эмиттера ниже. Все остальные транзисторы заперты, горит цифра 3.  Рис. 15. Схема диодно-резистивного дешифратора. Методами интегральной электроники дешифратор с высоковольтными ключевыми транзисторами может быть изготовлен в таком же корпусе, как и стандартные интегральные микросхемы (рис. 17). Рассматриваемая схема состоит из входных {1-4) и промежуточных (5-8) инверторов, формирующих управляющие сигналы, схем совпадения (9-12) на многоэмиттерных транзисторах и десяти выходных управляющих транзисторов - схем с открытым коллектором (13-22). Эмиттеры выходных транзисторов объединены в две группы - четные и нечетные. По эмиттерам четной группы управление осуществляется выходными сигналами промежуточного инвертора 5, по эмиттерам нечетной группы - сигналами входного инвертора /. Выходные сигналы схем совпадения управляют по базам выходными транзисторами В табл. б приведены состояния входов А, В, С, D и выходов Хо-Xs в зависимости от входных сигналов. Состояние логического О на выходе схемы соответствует отпертому выходному транзистору, а состояние логической I - запертому транзистору. На входы дешифратора поступают сигналы в коде 1-2-4-8. В зависимости от поступления входных сигналов один из десяти транзисторов отпирается, остальные транзисторы остаются запертыми Коллекторы выходных транзисторов соединяются с катодами цифровой индикаторной лампы. При отпирании выходного транзистора на катоде индикатора происходит понижение потенциала (до уровня приблизительно 2,5 В), достаточное для зажигания соответствующей цифры Для предотвращения пробоя выходных транзисторов коллекторы последних соединены с шиной О через стабилитроны, которые фиксируют потен-  L - Z J Рнс. 16. Схема резистивио-транзисторного дешифратора. циал коллектора запертого транзистора на уровне приблизительно 50 В Эмиттеры выходных транзисторов инверторов / и 5 соединены через диод с шиной О . При этом повышается потенциал иа эмиттерах соответствующей группы выходных транзисторов и обеспечивается их надежное запирание при низком потенциале на базе транзистора. Описываемая интегральная схема выполнена на основе транзисторно-транзисторной Л01ИКИ. По входным логическим уровням, напряжению питания (+5 В±10%) и конструкции корпуса эта схема подобна интегральным схемам серий 130, 133, 136. Мощность, потребляемая схемой, составляеп- 105 мВт.

ООО «Мягкий Дом» - это Отечественный производитель мебели. Наша профильная продукция - это диваны еврокнижка. Каждый диван можем изготовить в соответствии с Вашими пожеланияи (размер, ткань и материал). Осуществляем бесплатную доставку и сборку. Звоните! Ежедневно! (926)274-88-54 Продажа и изготовление мебели. Копирование контента сайта запрещено. Авторские права защищаются адвокатской коллегией г. Москвы. |

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||