(926)274-88-54

Бесплатная доставка.

Бесплатная сборка.

График работы:

Ежедневно. С 8-00 до 20-00.

Почта: soft_hous@mail.ru

|

Звоните! (926)274-88-54 Бесплатная доставка. Бесплатная сборка. |

Ассортимент тканей График работы: Ежедневно. С 8-00 до 20-00. Почта: soft_hous@mail.ru |

|

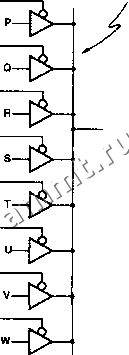

Читальный зал --> Программные средства foundation library IEEE; use IEEE.std.logic.1164.all; entity V74X148 is port ( EI L: in STD LOGIC; I L: in STD.LOGIC.VECTOR (7 downto 0); A.L: out STD.LOGIC.VECTOR (2 downto 0); EO.L, GS.L: out STD.LOGIC end V74X148; architecture V74xl48p of V74xl48 is signal EI: STD.LOGIC; - active-high version of input signal I: STD.LOGIC.VECTOR (7 downto 0); - active-high version of inputs signal EO, GS: STD.LOGIC; ~ active-high version of outputs signal A: STD.LOGIC.VECTOR (2 downto 0); ~ active-high version of outputs begin process (EI.L, I L, EI, EO, GS, I, A) variable j: INTEGER range 7 downto 0; begin EI <= not EI.L; - convert input I <= not I.L; - convert inputs EO <= Ч ; GS <= 0 ; A <= ООО ; if (EI)=0 then EO <= 0 ; else for j in 7 downto 0 loop if I(j) = 4 then GS <= 1; EO <= 0; A <= COSV.STD.LOGIC.VECTQRCj,3); exit; end if; end loop; end if; EO.L <= not EO; - convert output GS.L <= not GS; - convert output A.L <= not A; - convert outputs end process; end V74xl48p; Табл. 5.26 представляет собой поведенческую программу на языке VHDL для приоритетного шифратора, эквивалентного шифратору 74x148. В ней используется цикл FOR для поиска активизированного входа, начиная со входа с высшим 5.5.4. Описание шифраторов на языке VHDL На языке VHDL шифраторы описываются так же, как и на языке ABEL. Мы можем ввести в программу на языке VHDL эквивалент таблицы истинности или явную запись соотношений, но гораздо нагляднее поведенческое описание шифратора. Так как в языке VHDL логическая конструкция IF-THEN-ELSE лучше всего описывает назначение приоритетов и доступна только в пределах процесса, мы применим поведенческий подход, ориентированный на использование процессов. Табл. 5.26. Поведенческая программа на языке VHDL для 8-входового приоритетного шифратора типа 74x148 гфиоритетом. Подобно неюторым нашим предыдущим программам, в начале и в конце программы выполняется явное преобразование активного уровня. Кроме того, вспомните, что в разделе 4.7.4 была определена функция CONV STD LOGIC VECTOR {j , п) преобразования целого числа j в вектор STD LOGIC VECTOR заданной длины п. Эту программу легко модифицировать, если нужно задать приоритеты в другом порядке или изменить число входов, а также с целью расширения функциональных возможностей типа обнаружения входа, имеющего второй по старшинству уровень приоритета , о чем будет рассказано в разделе 6.2.3. 5.6. Устройства стремя состояниями в разделах 3.7.3 и 3.10.5 были описаны электрические схемы КМОП- и ТТЛ-устройств, выходы юторых могут находиться в одном из трех состояний: 0,1 и Hi-Z. В этом параграфе мы покажем, как применять такие устройства. 5.6.1. Буферы с тремя состояниями Основным устройством с тремя состояниями является буфер с тремя состояниями (three-state buffer), который часто называют драйвером с тремя состояниями (three-state driver). На рис. 5.53 показаны условные обозначения четырех конструктивно различных буферов с тремя состояниями. На рис. (а) и (Ь) изображены неинвертирующие буферы, а на рис. (с) и (d) - инверторы. У схемы с тремя состояниями имеется вход разрешения (three-state enable), указываемый в условном обозначении свер?. Когда на этот вход подан сигнал разрешения, который может иметь высокий активный уровень [рис. (а) и (с)] или низкий активный уровень [рис. (Ь) и (d)], устройство ведет себя как обыкновенный буфер или инвертор. Когда сигнал на входе разрешения имеет неактивный уровень, выход устройства становится плавающим , то есть переходит в высоко им педансное, разомкнутое состояние (Hi-Z) и функционально ведет себя так, как будто там ничего нет. (а) (Ь) (с) (d) Рис. 5.53. Различные буферы с тремя состояниями: (а) неинвертируюш1й, с высоким активным уровнем сигнала разрешения; (Ь) неинвертируюшяй, с низким активным уровнем сигнала разрешения; (с) инвертирующий, с высоким активным уровнем сигнала разрешения; (d) инвертирующий, с низким активным уровнем сигнала разрешения Устройства с тремя состояниями позволяют нескольким источникам совместно использовать одну линию коллективного пользования при условии, что в это время на линии говорит только одно устройство. На рис. 5.54 приведен пример, как это можно сделать. Тремя входными битами SSRG2-SSRC0 выбирается один из восьми источников данных, который может выдавать сигналы на единственную линию SDATA. Дешифратор 3x8 типа 74x138 обеспечивает на данном о-зке вре- мени активизацшо сигнала только на одной из восьми линий SEL, разрешая только одному буферу с тремя состояниями выдавать данные на линию SDATA. Но если активный уровень присутствует не на всех входах EN, то все буферы остаются в третьем состоянии. В этом случае логическое значение на линии SDATA не определено. 1-разрядная линия коллективного пользования 74x138

YO Y1 Y2 Y3 Y4 Y5 Y6 Y7b . 15 SELP L 14 SELQ L 13 SELR L 12 SELS L 11 SELTJ. 10 SELUL . 9 SELV L SELW.L SDATA  Рис, 5.54. Восемь источников сигналов с тремя состояниями, совместно использующих линию коллективного пользования Типичные устройства с тремя состояниями создаются так, чтобы переход в состояние Hi-Z происходил быстрее, чем выход из этого состояния. (В обозначениях, принятых в справочных данных, обе величины t и меньше, чем значения pZL pZH также раздел 3.7.3.) Это означает, что в случае, когда выходы двух устройств с тремя состояниями подключены к одной и той же линии коллективного пользования и мы одновременно переводим в третье состояние одно из устройств и выводим из этого состояния другое устройство, первое устройство отключается от линии коллективного пользования прежде, чем будет подключено второе. Это важный момент. Действительно, если бы оба устройства одновременно были открыты и попытались установить на линии противоположные значения выходных сигналов (О и 1), то в системе потек бы чрезмерно большой ток, создавая помехи (см. раздел 3.7.7). Когда такая сшуащм возникает, ее часто называют борьбой (fighting). ООО «Мягкий Дом» - это Отечественный производитель мебели. Наша профильная продукция - это диваны еврокнижка. Каждый диван можем изготовить в соответствии с Вашими пожеланияи (размер, ткань и материал). Осуществляем бесплатную доставку и сборку. Звоните! Ежедневно! (926)274-88-54 Продажа и изготовление мебели. Копирование контента сайта запрещено. Авторские права защищаются адвокатской коллегией г. Москвы. |